# **User Manual**

# APM32F405/415xG

## APM32F407/417xExG

Arm<sup>®</sup> Cortex<sup>®</sup>-M4F based 32-bit MCU

Version: V2.2

© Geehy Semiconductor Co., Ltd.

## Contents

| 1    | Introduction and document description rules     | 8    |

|------|-------------------------------------------------|------|

| 1.1  | Introduction                                    | 8    |

| 1.2  | Document description rules                      | 8    |

| 2    | System architecture                             | 12   |

| 2.1  | Full name and abbreviation description of terms | . 12 |

| 2.2  | System architecture block diagram               | . 12 |

| 2.3  | Memory mapping                                  | . 15 |

| 2.4  | Startup configuration                           | . 16 |

| 3    | FLASH memory                                    | 18   |

| 3.1  | Full name and abbreviation description of terms | . 18 |

| 3.2  | Introduction                                    | . 18 |

| 3.3  | Main characteristics                            | . 18 |

| 3.4  | Flash memory structure                          | . 19 |

| 3.5  | Flash memroy functional description             | . 19 |

| 3.6  | Register address mapping                        | .26  |

| 3.7  | Register functional description                 | .26  |

| 4    | External Memory Controller (EMMC)               | 31   |

| 4.1  | Full name and abbreviation description of terms | . 31 |

| 4.2  | EMMC Overview                                   | .31  |

| 4.3  | SMC Introduction                                | . 31 |

| 4.4  | SMC Structure Block Diagram                     | . 32 |

| 4.5  | SMC Functional Description                      | . 32 |

| 4.6  | SMC register address mapping                    | . 38 |

| 4.7  | SMC register functional description             | . 38 |

| 4.8  | DMC introduction                                | .48  |

| 4.9  | Main characteristics of DMC                     | .48  |

| 4.10 | DMC structure block diagram                     | .49  |

| 4.11 | DMC functional description                      | .49  |

| 4.12 | DMC register address mapping                    |      |

| 4.13 | DMC register functional description             | .51  |

| 5    | System configuration controller (SYSCFG)        | 56   |

| 5.1  | Main characteristics                            | . 56 |

| 5.2  | I/O compensation cell                           | . 56 |

| 5.3  | Register address mapping                        | . 56 |

| 5.4  | Register functional description                 | . 56 |

| 6    | Reset and clock (RCM)                           | 61  |

|------|-------------------------------------------------|-----|

| 6.1  | Full name and abbreviation description of terms | 61  |

| 6.2  | Reset management unit (RMU)                     | 61  |

| 6.3  | Clock management unit (CMU)                     | 64  |

| 6.4  | Register address mapping                        | 71  |

| 6.5  | Register functional description                 | 72  |

| 7    | Power management unit (PMU)                     |     |

| 7.1  | Full name and abbreviation description of terms |     |

| 7.2  | Introduction                                    |     |

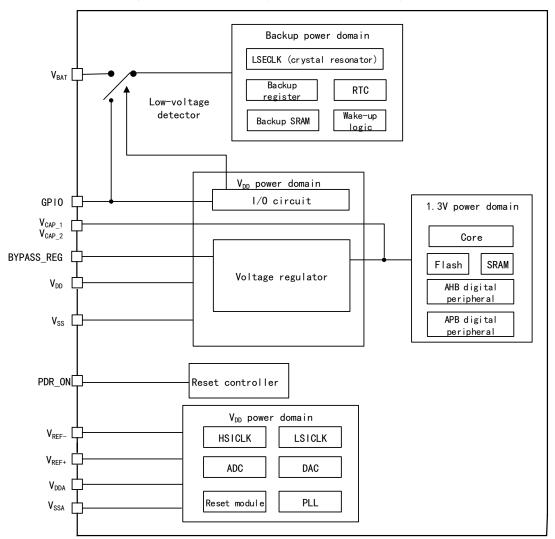

| 7.3  | Structure block diagram                         |     |

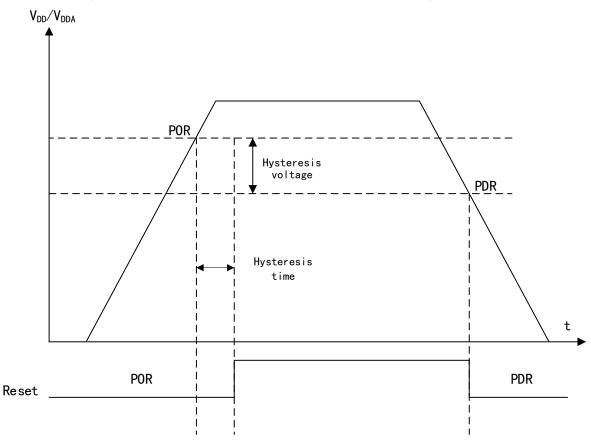

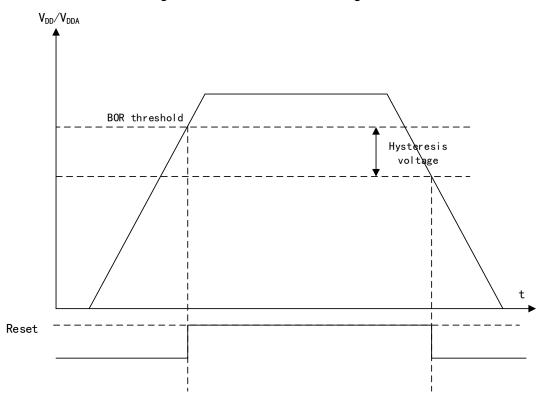

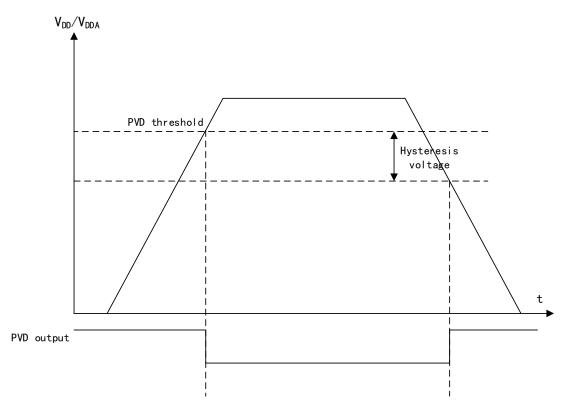

| 7.4  | Functional description                          |     |

| 7.5  | Register address mapping                        |     |

| 7.6  | Register functional description                 |     |

| 8    | Nested vector interrupt controller (NVIC)       | 112 |

| 8.1  | Full name and abbreviation description of terms | 112 |

| 8.2  | Introduction                                    | 112 |

| 8.3  | Main characteristics                            | 112 |

| 8.4  | Interrupt and exception vector table            | 112 |

| 9    | External Interrupt/Event Controller (EINT)      | 120 |

| 9.1  | Introduction                                    |     |

| 9.2  | Main Characteristics                            |     |

| 9.3  | Functional description                          | 120 |

| 9.4  | Register address mapping                        |     |

| 9.5  | Register functional description                 |     |

| 10   | Direct memory access (DMA)                      |     |

| 10.1 | Introduction                                    | 126 |

| 10.2 | Main characteristics                            |     |

| 10.3 | Functional description                          |     |

| 10.4 | DMA register address mapping                    |     |

| 10.5 | Register functional description                 |     |

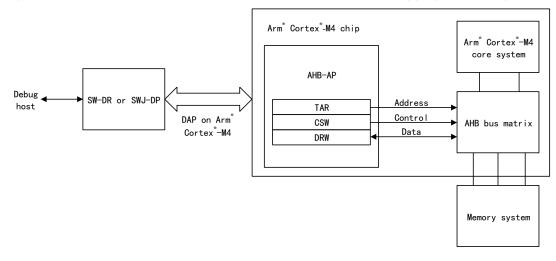

| 11   | Debug MCU (DBGMCU)                              | 142 |

| 11.1 | Full name and abbreviation description of terms | 142 |

| 11.2 | Introduction                                    | 142 |

| 11.3 | Main characteristics                            | 142 |

| 11.4 | Functional description                          | 143 |

| 11.5 | Register address mapping                        | 144 |

| 11.6 | Register functional description                 | 144 |

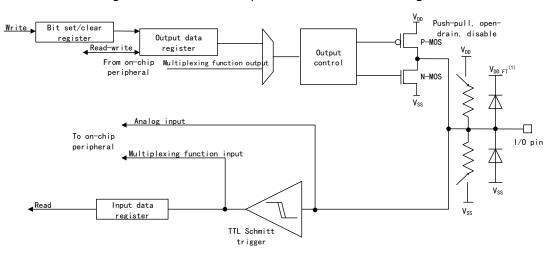

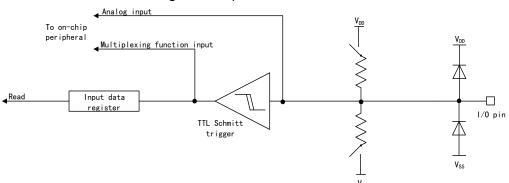

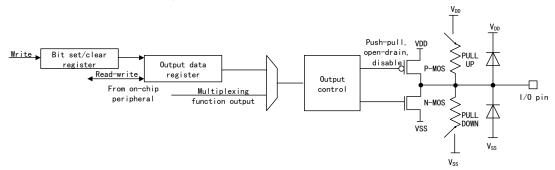

| 12    | General-Purpose Input/Output Pin (GPIO)         | 150 |

|-------|-------------------------------------------------|-----|

| 12.1  | Full name and abbreviation description of terms | 150 |

| 12.2  | Main characteristics                            | 150 |

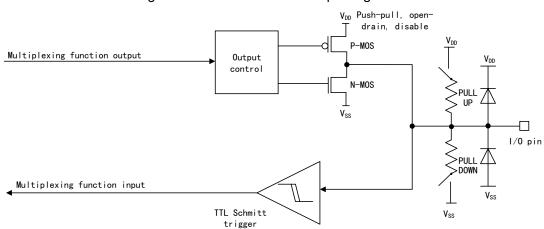

| 12.3  | Structure block diagram                         | 151 |

| 12.4  | Functional description                          | 151 |

| 12.5  | Register address mapping                        | 155 |

| 12.6  | Register functional description                 | 155 |

| 13    | Timer overview                                  | 160 |

| 13.1  | Full name and abbreviation description of terms | 160 |

| 13.2  | Timer category and main difference              | 160 |

| 14    | Advanced Timers (TMR1/8)                        | 163 |

| 14.1  | Introduction                                    | 163 |

| 14.2  | Main characteristics                            | 163 |

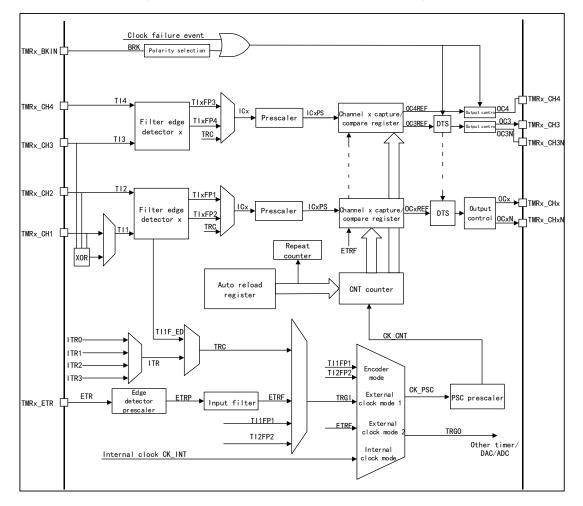

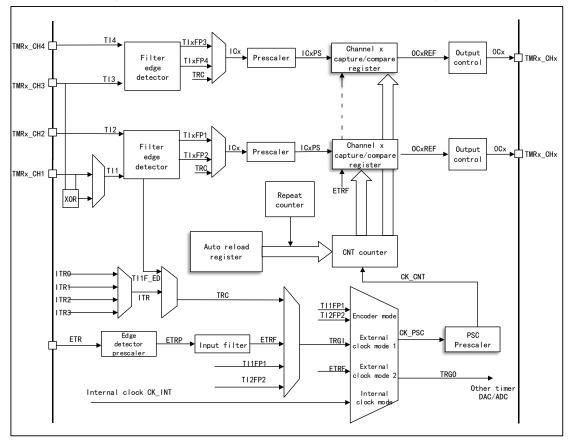

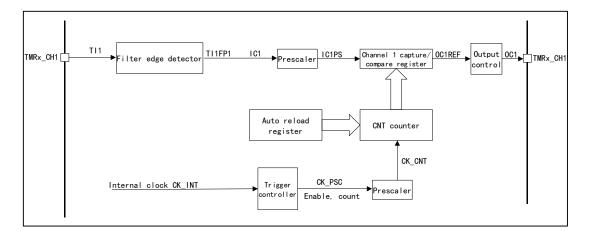

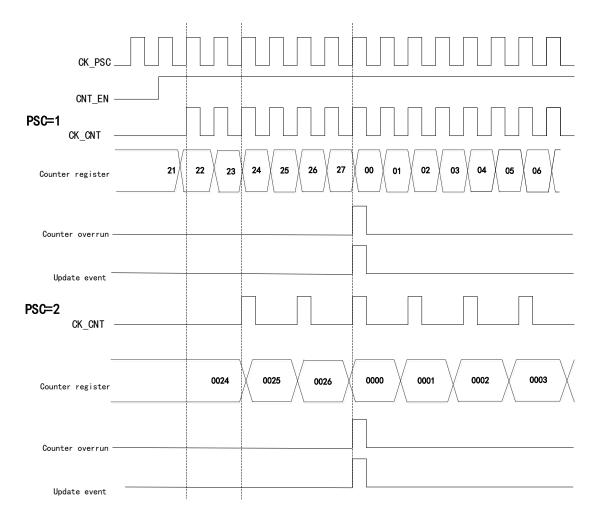

| 14.3  | Structure block diagram                         | 164 |

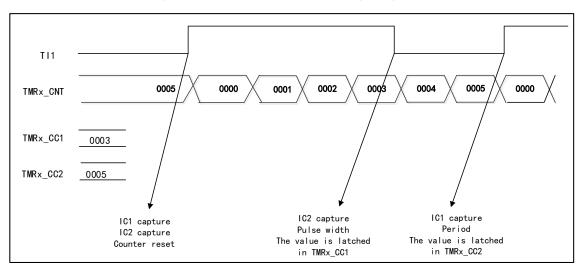

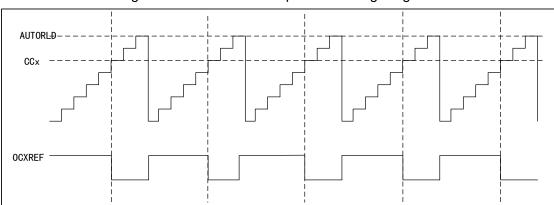

| 14.4  | Functional description                          | 164 |

| 14.5  | Register address mapping                        | 181 |

| 14.6  | Register functional description                 | 182 |

| 15    | General-purpose timer (TMR2/3/4/5)              | 201 |

| 15.1  | Introduction                                    | 201 |

| 15.2  | Main characteristics                            | 201 |

| 15.3  | Structure block diagram                         | 202 |

| 15.4  | Functional description                          | 202 |

| 15.5  | Register address mapping                        | 215 |

| 15.6  | Register functional description                 | 216 |

| 16    | General-purpose timer (TMR9/10/11/12/13/14)     | 232 |

| 16.1  | Introduction                                    | 232 |

| 16.2  | Main characteristics of TMR9/12                 | 232 |

| 16.3  | Main characteristics of TMR10/11/13/14          | 232 |

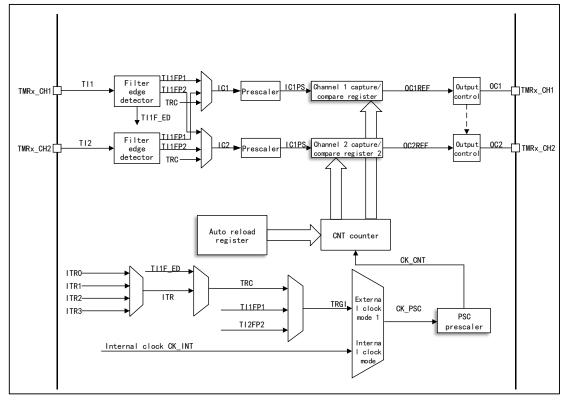

| 16.4  | TMR9/12 structure block diagram                 | 233 |

| 16.5  | TMR10/11/13/14 structure block diagram          | 234 |

| 16.6  | Functional description                          | 234 |

| 16.7  | TMR9/12 register address mapping                | 239 |

| 16.8  | TMR9/12 register functional description         | 240 |

| 16.9  | TMR10/11/13/14 register address mapping         | 249 |

| 16.10 | TMR10/11/13/14 register functional description  | 249 |

| 17    | Basic timer (TMR6/7)                            | 257 |

| 17.1  | Introduction                                    | 257 |

| 17.2 | Main characteristics                                   | 257 |

|------|--------------------------------------------------------|-----|

| 17.3 | Structure block diagram                                | 257 |

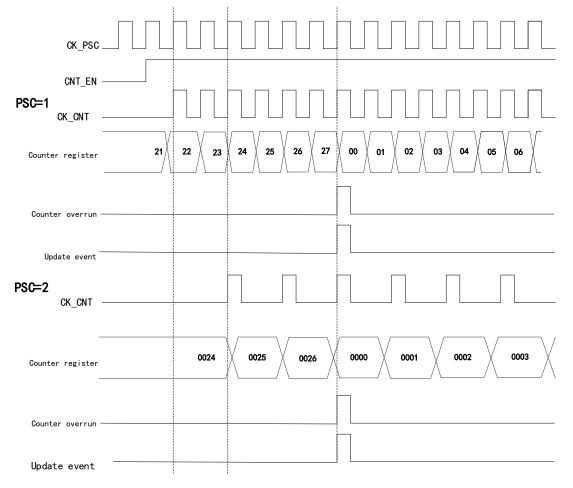

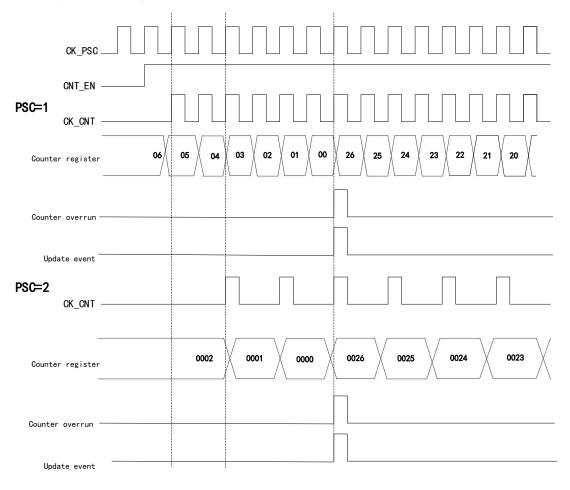

| 17.4 | Functional description                                 | 257 |

| 17.5 | Register address mapping                               | 259 |

| 17.6 | Register functional description                        | 260 |

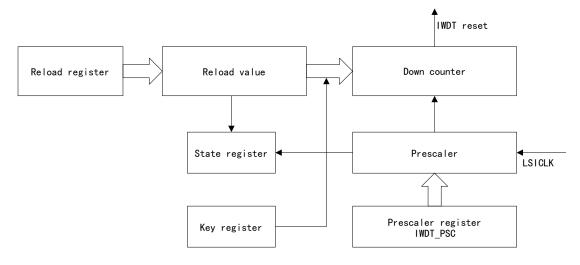

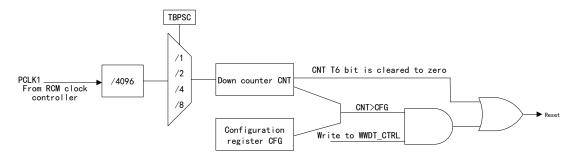

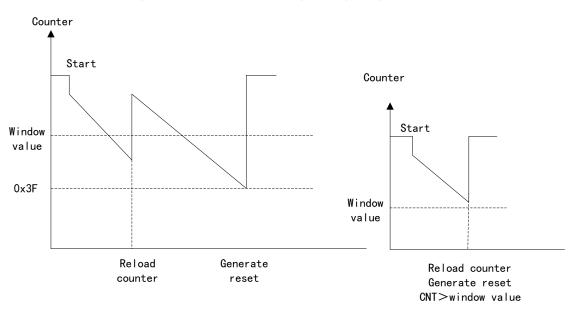

| 18   | Watchdog timer (WDT)                                   | 264 |

| 18.1 | Introduction                                           | 264 |

| 18.2 | Independent watchdog timer (IWDT)                      | 264 |

| 18.3 | Window watchdog timer (WWDT)                           | 266 |

| 18.4 | IWDT register address mappin                           | 267 |

| 18.5 | IWDT register functional description                   | 268 |

| 18.6 | WWDT register address mappin                           | 269 |

| 18.7 | WWDT register functional description                   | 269 |

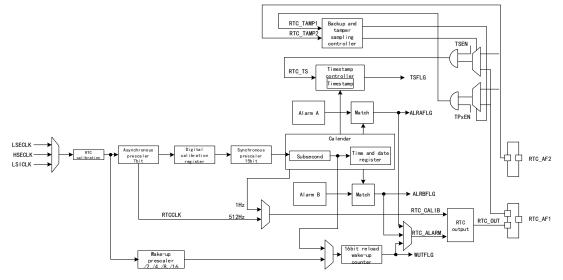

| 19   | Real-time clock (RTC)                                  | 271 |

| 19.1 | Full name and abbreviation description of terms        | 271 |

| 19.2 | Introduction                                           | 271 |

| 19.3 | Main characteristics                                   | 271 |

| 19.4 | Structure block diagram                                | 271 |

| 19.5 | Functional description                                 | 272 |

| 19.6 | Register address mapping                               | 278 |

| 19.7 | Register functional description                        | 279 |

| 20   | HASH processor (HASH)                                  | 295 |

| 20.1 | Introduction                                           | 295 |

| 20.2 | Main characteristics                                   | 295 |

| 20.3 | Functional description                                 | 295 |

| 20.4 | Register address mapping                               | 296 |

| 20.5 | Register functional description                        | 296 |

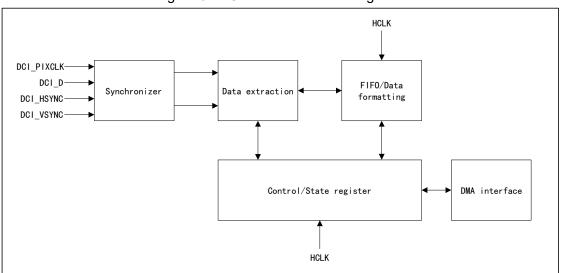

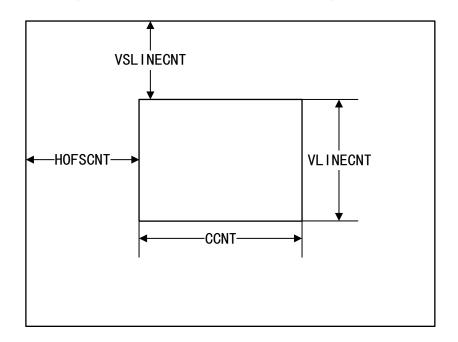

| 21   | Digital camera interface (DCI)                         | 301 |

| 21.1 | Full name and abbreviation description of terms        | 301 |

| 21.2 | Introduction                                           | 301 |

| 21.3 | Main characteristics                                   | 301 |

| 21.4 | Structure block diagram                                | 302 |

| 21.5 | Functional description                                 | 302 |

| 21.6 | Register address mapping                               | 306 |

| 21.7 | Register functional description                        | 307 |

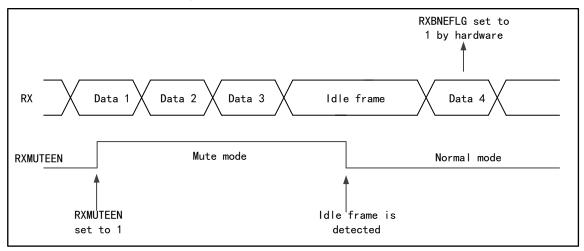

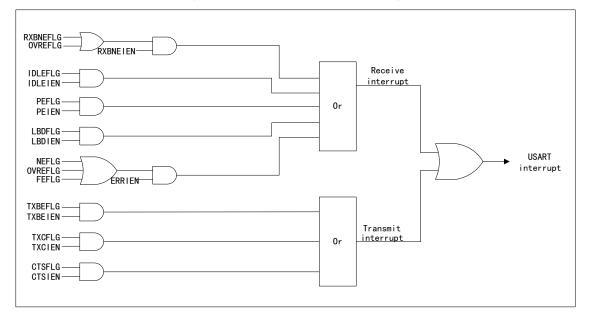

| 22   | Universal synchronous/asynchronous transceiver (USART) | 313 |

| 22.1 | Full name and abbreviation description of terms        | 313 |

| 22.2 | Introduction                                                  | 313 |

|------|---------------------------------------------------------------|-----|

| 22.3 | Main characteristics                                          | 313 |

| 22.4 | Functional description                                        | 315 |

| 22.5 | Register address mapping                                      | 329 |

| 22.6 | Register functional description                               | 329 |

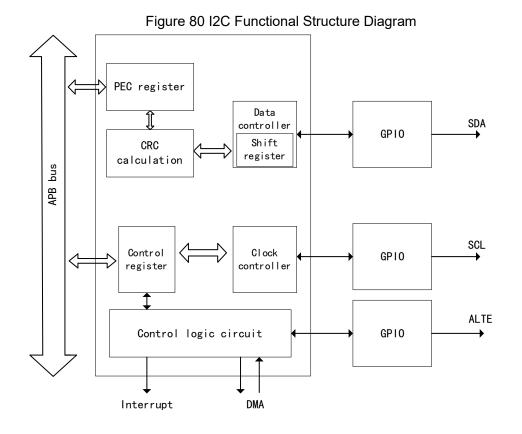

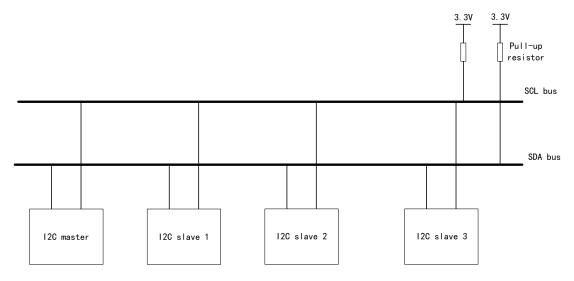

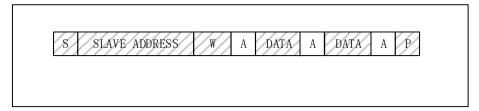

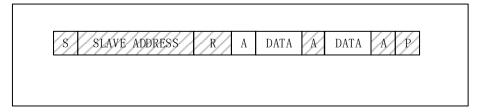

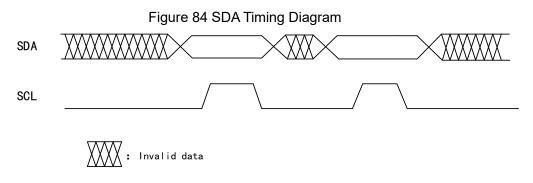

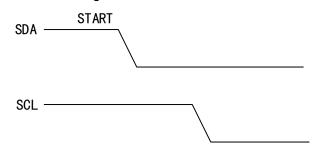

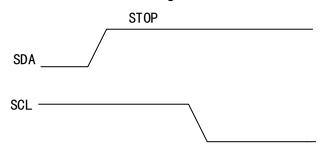

| 23   | Internal integrated circuit interface (I2C)                   | 337 |

| 23.1 | Full name and abbreviation description of terms               | 337 |

| 23.2 | Introduction                                                  | 337 |

| 23.3 | Main characteristics                                          | 337 |

| 23.4 | Structure block diagram                                       | 339 |

| 23.5 | Functional description                                        | 339 |

| 23.6 | Register address mapping                                      | 346 |

| 23.7 | Register functional description                               | 346 |

| 24   | Serial peripheral interface/On-chip audio interface (SPI/I2S) | 356 |

| 24.1 | Full name and abbreviation description of terms               | 356 |

| 24.2 | Introduction                                                  | 356 |

| 24.3 | Main characteristics                                          | 357 |

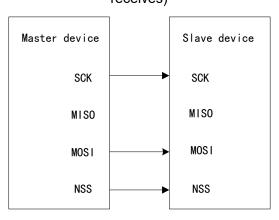

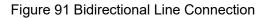

| 24.4 | SPI functional description                                    | 358 |

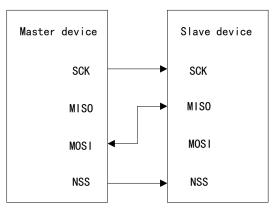

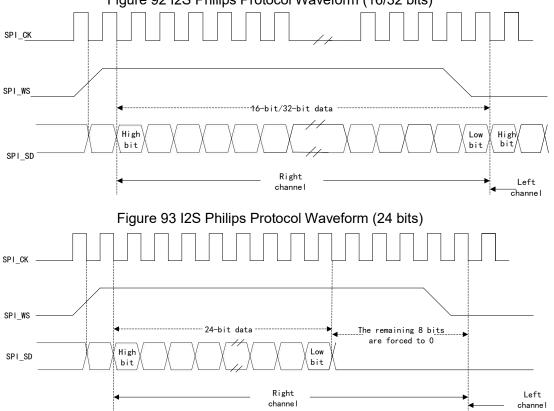

| 24.5 | I2S functional description                                    | 369 |

| 24.6 | Register address mapping                                      | 381 |

| 24.7 | Register functional description                               | 382 |

| 25   | Controller area network (CAN)                                 | 389 |

| 25.1 | Full name and abbreviation description of terms               | 389 |

| 25.2 | Introduction                                                  | 389 |

| 25.3 | Main characteristics                                          | 389 |

| 25.4 | Functional description                                        | 389 |

| 25.5 | Register address mapping                                      | 398 |

| 25.6 | Register functional description                               | 399 |

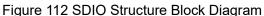

| 26   | Secure digital input/output interface (SDIO)                  | 417 |

| 26.1 | Full name and abbreviation description of terms               | 417 |

| 26.2 | Introduction                                                  | 417 |

| 26.3 | Main characteristics                                          | 417 |

| 26.4 | Functional description                                        | 417 |

| 26.5 | Register address mapping                                      | 440 |

| 26.6 | Register functional description                               | 440 |

| 27   | USB_OTG                                                       | 452 |

| 27.1 | Introduction                                                  | 452 |

| 27.2  | OTG_FS global register address mapping                                  | .452  |

|-------|-------------------------------------------------------------------------|-------|

| 27.3  | OTG_FS global register functional description                           | .453  |

| 27.4  | OTG_FS host mode register address mapping                               | .467  |

| 27.5  | OTG_FS host mode register functional description                        | .468  |

| 27.6  | OTG_FS device mode register address mapping                             | .474  |

| 27.7  | OTG_FS device mode register functional description                      | .475  |

| 27.8  | Full-speed OTG power and clock gating control register (OTG_FS_PCGCTRL) | 490   |

| 27.9  | OTG_HS1 global register address mapping                                 | .491  |

| 27.10 | OTG_HS1 global register functional description                          | .492  |

| 27.11 | OTG_HS1 host mode register address mapping                              | . 509 |

| 27.12 | OTG_HS1 host mode register functional description                       | . 509 |

| 27.13 | OTG_HS1 device mode register address mapping                            | .517  |

| 27.14 | OTG_HS1 device mode register functional description                     | .518  |

| 27.15 | High-speed OTG power and clock gating control register                  |       |

| (OTG  | _HS1_PCGCTRL)                                                           | . 536 |

| 27.16 | OTG_HS2 register address mapping                                        | . 537 |

| 27.17 | OTG_HS2 global register functional description                          | . 537 |

| 28    | Ethernet                                                                | 539   |

| 28.1  | Introduction                                                            | . 539 |

| 28.2  | Main characteristics of Ethernet                                        | . 539 |

| 28.3  | Functional description                                                  | . 542 |

| 28.4  | MAC register address mapping                                            | .571  |

| 28.5  | MAC register functional description                                     | . 572 |

| 28.6  | MMC register address mapping                                            | . 588 |

| 28.7  | MMC register functional description                                     | . 588 |

| 28.8  | PTP register address mapping                                            | . 592 |

| 28.9  | PTP register functional description                                     | . 592 |

| 28.10 | DMA register address mapping                                            | . 597 |

| 28.11 | DMA register functional description                                     | . 597 |

| 29    | Analog-to-digital converter (ADC)                                       | 609   |

| 29.1  | Full name and abbreviation description of terms                         | .609  |

| 29.2  | Introduction                                                            | .610  |

| 29.3  | Main characteristics                                                    | .610  |

| 29.4  | Functional description                                                  | . 611 |

| 29.5  | Register address mapping                                                |       |

| 29.6  | Register functional description                                         | .623  |

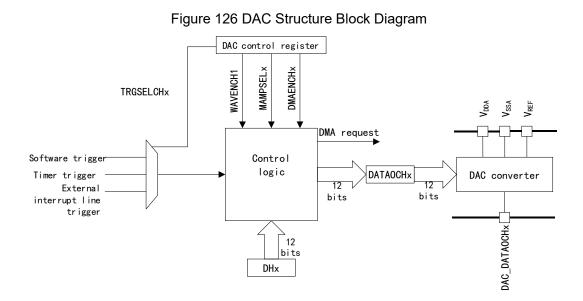

| 30    | Digital-to-analog converter (DAC)                                       | 634   |

| 30.1  | Full name and abbreviation description of terms                         |       |

|       | ·                                                                       |       |

| 30.2 | Introduction                                 | 634   |

|------|----------------------------------------------|-------|

| 30.3 | Structure block diagram                      | 634   |

| 30.4 | Functional description                       | 634   |

| 30.5 | Register address mapping                     | 638   |

| 30.6 | Register functional description              | 638   |

| 31   | Random number generator (RNG)                | . 644 |

| 31.1 | Introduction                                 | 644   |

| 31.2 | Main characteristics                         | 644   |

| 31.3 | Functional description                       | 644   |

| 31.4 | Register address mapping                     | 645   |

| 31.5 | Register functional description              | 645   |

| 32   | CRYP                                         | . 648 |

| 32.1 | Introduction                                 | 648   |

| 32.2 | Main characteristics                         | 648   |

| 32.3 | Interrupt                                    | 648   |

| 32.4 | DMA                                          | 649   |

| 32.5 | Register address mapping                     | 649   |

| 32.6 | Register functional description              | 649   |

| 33   | Cyclic redundancy check computing unit (CRC) | . 654 |

| 33.1 | Introduction                                 | 654   |

| 33.2 | Functional description                       | 654   |

| 33.3 | Register address mapping                     | 654   |

| 33.4 | Register functional description              | 654   |

| 34   | Chip electronic signature                    | . 656 |

| 34.1 | Introduction                                 | 656   |

| 34.2 | Register functional description              | 656   |

| 35   | Version History                              | . 657 |

|      |                                              |       |

## **1** Introduction and document description rules

## 1.1 Introduction

This user manual provides application developers with all the information about how to use MCU (micro-controller) system architecture, memory and peripherals.

For information about Arm<sup>®</sup> Cortex<sup>®</sup>-M4F core, please refer to *Arm<sup>®</sup> Cortex<sup>®</sup>* - *M4F Technical Reference Manual*; please refer to the corresponding datasheet for detailed data such as model information, dimension and electrical characteristics of the device; for all MCU series models, please refer to the corresponding datasheet for memory mapping, peripheral existence and their number.

It is hereby declared that Geehy Semiconductor Co., Ltd., hereinafter refer to as "Geehy".

## **1.2 Document description rules**

#### 1.2.1 "Register functional description" rules

- (1) Control (CTRL) registers are all "set to 1 and cleared to 0 by software", unless otherwise specified.

- (2) The control registers are usually followed by verb abbreviations to make a distinction. The verbs can be: EN-Enable, CFG-Configure, D-Disable, SET-Setup and SEL-Select

- (3) The state register abbreviation is usually followed by FLG to make a difference.

- (4) The value and data registers usually include V, VALUE, D and DATA, which are not followed by verbs, such as: xxPSC and CNT.

#### 1.2.2 Full name and abbreviation description of terms

| R/W mode   | Description                                                       | Abbreviation |  |

|------------|-------------------------------------------------------------------|--------------|--|

| read/write | Software can read and write this bit.                             | R/W          |  |

| read-only  | Software can only read this bit.                                  | R            |  |

| write-only | Software can only write this bit, and after reading this bit, the | W            |  |

| write-only | reset value will be returned.                                     | vv           |  |

| read/clear | The software can read this bit and clear it by writing 1. Writing | RC W1        |  |

| Teau/clear | 0 has no effect on this bit.                                      | KC_WI        |  |

| read/clear | The software can read this bit and clear it by writing 0. Writing | RC W0        |  |

| reau/clear | 1 has no effect on this bit.                                      | NC_W0        |  |

#### Table 1 Abbreviation and Description of R/W Modes

| R/W mode                | Description                                                        | Abbreviation |

|-------------------------|--------------------------------------------------------------------|--------------|

| road/alaar by road      | The software can read this bit and reading this bit will           |              |

| read/clear by read      | automatically clear it to 0, and writing this bit is invalid.      | RC_R         |

| read/set                | The software can read and set this bit, and writing 0 has no       | R/S          |

| read/set                | effect on this bit.                                                | K/3          |

| road aphywrite trigger  | The software can read this bit and writing 0 or 1 can trigger an   |              |

| read-only write trigger | event but has no effect on the value of this bit.                  | RT_W         |

| togglo                  | The software can flip this bit only by writing 1 and writing 0 has | т            |

| toggle                  | no effect on this bit.                                             | 1            |

# Table 2 Functional Description and Full Name and Abbreviation of Terms of CommonlyUsed Registers

| Full name in English | English abbreviation |

|----------------------|----------------------|

| Enable               | EN                   |

| Disable              | D                    |

| Clear                | CLR                  |

| Select               | SEL                  |

| Configure            | CFG                  |

| Contri               | CTRL                 |

| Controller           | С                    |

| Reset                | RST                  |

| Stop                 | STOP                 |

| Set                  | SET                  |

| Load                 | LD                   |

| Calibration          | CAL                  |

| Initialize           | INIT                 |

| Error                | ERR                  |

| Status               | STS                  |

| Ready                | RDY                  |

| Software             | SW                   |

| Hardware             | HW                   |

| Source               | SRC                  |

| System               | SYS                  |

| Peripheral           | PER                  |

| Address              | ADDR                 |

| Direction            | DIR                  |

| Full name in English | English abbreviation |

|----------------------|----------------------|

| Clock                | CLK                  |

| Input                | I                    |

| Output               | 0                    |

| Interrupt            | INT                  |

| Data                 | DATA                 |

| Size                 | SIZE                 |

| Divider              | DIV                  |

| Prescaler            | PSC                  |

| Multiplier           | MUL                  |

| Period               | PRD                  |

#### Table 3 Full Name and Abbreviation of Modules

| Full name in English                                    | English abbreviation |

|---------------------------------------------------------|----------------------|

| External Memory Controller                              | EMMC                 |

| Static Memory Controller                                | SMC                  |

| Dynamic memory Controller                               | DMC                  |

| Reset and Clock Management Unit                         | RCM                  |

| Power Management Unit                                   | PMU                  |

| Backup Register                                         | BAKPR                |

| Nested Vector Interrupt Controller                      | NVIC                 |

| External Interrupt /Event Controller                    | EINT                 |

| Direct Memory Access                                    | DMA                  |

| Debug MCU                                               | DBG MCU              |

| General-Purpose Input Output Pin                        | GPIO                 |

| Alternate Function Input Output Pin                     | AFIO                 |

| Timer                                                   | TMR                  |

| Watchdog Timer                                          | WDT                  |

| Independent Watchdog Timer                              | IWDT                 |

| Windows Watchdog Timer                                  | WWDT                 |

| Real-Time Clock                                         | RTC                  |

| Universal Synchronous Asynchronous Receiver Transmitter | USART                |

| Inter-Integrated Circuit Interface                      | I2C                  |

| Serial Peripheral Interface                             | SPI                  |

| Full name in English                     | English abbreviation |

|------------------------------------------|----------------------|

| Inter-IC Sound Interface                 | 128                  |

| Quad Serial Peripheral Interface         | QSPI                 |

| Controller Area Network                  | CAN                  |

| Secure Digital Input and Output          | SDIO                 |

| Universal Serial Bus Full-Speed Device   | USBD                 |

| Analog-to-Digital Converter              | ADC                  |

| Digital-to-Analog Converter              | DAC                  |

| Cyclic Redundancy Check Calculation Unit | CRC                  |

| Float Point Unit                         | FPU                  |

## 2 System architecture

## 2.1 Full name and abbreviation description of terms

| Full name in English          | English abbreviation |

|-------------------------------|----------------------|

| Advanced High-Performance Bus | AHB                  |

| Advanced Peripheral Bus       | APB                  |

| Core Couple Memory            | ССМ                  |

Table 4 Full name and abbreviation description of terms

## 2.2 System architecture block diagram

Arm<sup>®</sup> Cortex<sup>®</sup>-M4F core in the product has FPU, while the FPU of other series of products (unless otherwise specified) is beyond the core.

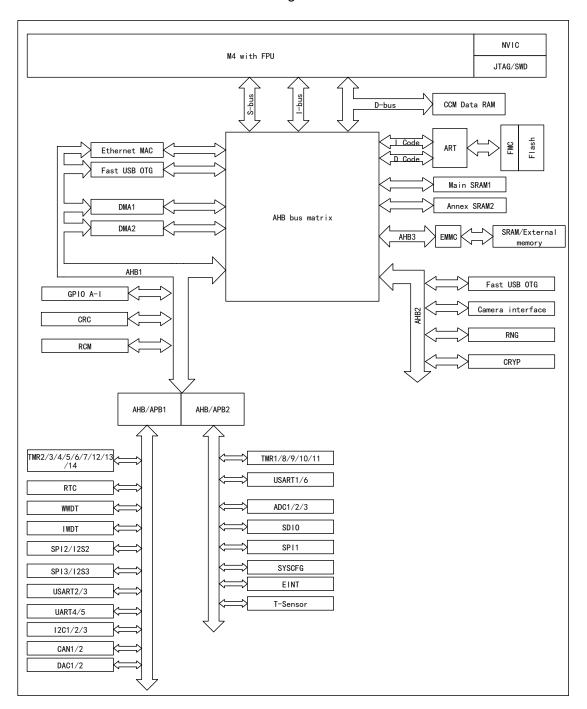

The system mainly consists of eight master modules and seven slave modules.

The master modules are I-bus, D-bus and S-bus of Arm<sup>®</sup> Cortex<sup>®</sup>-M4F core with FPU, general-purpose DMA1, general-purpose DMA2, and DMA2 peripheral bus, Ethernet DMA bus and USB OTG HS DMA bus.

The slave modules are internal Flash I-bus, D-bus, main internal memory SRAM1, auxiliary internal memory SRAM2, AHB1 bus and AHB1/APB bridge connected peripherals, peripherals on AHB2 bus and EMMC.

The bus matrix provides a platform to support the master module to access the slave module. The matrix can realize concurrent access, and the CPU still has efficient processing capacity when multiple peripherals are running at high speed.

It also has a 64-bit core couple memory, and it can access only through CPU.

The name and description of the bus are shown in the following table.

| Name           | Description                                                                                       |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| l-bus          | Connect the instruction bus of Arm <sup>®</sup> Cortex <sup>®</sup> -M4F core and the bus matrix. |  |  |  |  |

| I-bus          | Used for obtaining instructions.                                                                  |  |  |  |  |

| D-bus          | Connect the data bus of Arm <sup>®</sup> Cortex <sup>®</sup> -M4F core and the bus matrix.        |  |  |  |  |

| D-bus          | Used for text loading and debugging access.                                                       |  |  |  |  |

| S-bus          | Connect the system bus of Arm <sup>®</sup> Cortex <sup>®</sup> -M4F core and the bus matrix.      |  |  |  |  |

| S-bus          | Used for accessing the data in peripherals and SRAM.                                              |  |  |  |  |

|                | Connect the main interface of DMA memory and the bus matrix.                                      |  |  |  |  |

| DMA memory bus | Realize transmission related to the memory through DMA.                                           |  |  |  |  |

#### Table 5 Bus Name

| Name               | Description                                                               |

|--------------------|---------------------------------------------------------------------------|

|                    | Connect the main interface of DMA peripherals and the bus matrix.         |

| DMA peripheral bus | It can not only realize access of DMA to the peripherals on AHB, but also |

|                    | realize transmission among memories.                                      |

| Ethernet DMA bus   | Connect the main interface of Ethernet DMA and the bus matrix.            |

| Ethemet DiviA bus  | The data are loaded/stored in the memory through Ethernet DMA.            |

| USB OTG HS DMA     | Connect the main interface of USB OTG HS DMA and the bus matrix.          |

| bus                | The data are loaded/stored in the memory through USB OTG DMA.             |

| Bus matrix         | Coordinate the access among modules, and roll polling algorithm is used   |

| Dus mauix          | during arbitration.                                                       |

|                    | The bridge provides synchronous connection between AHB and APB buses.     |

| AHB/APB bridge     | The non-32-bit access to APB register will be converted into 32 bits      |

|                    | automatically.                                                            |

#### Figure 1 APM32F405/415xG、 APM32F407/417xExG System Architecture Block

Diagram

Note:

APM32F415xG/APM32F417xExG has HASH processor and CRYP, while APM32F405xG/APM32F407xExG do not have; APM32F407/417xExG (except APM32F407RxT6) has Ethernet and DCI, while APM32F405/415xG and APM32F407RxT6 do not have.

- (2) Actually, APM32F405/415xG、APM32F407/417xExG series has two USB OTG\_HS, and they share the clock, reset, bus address, CPU interrupt, power supply, pins and other related resources. Only one of two USB OTG\_HS can be used at the same time. Their difference is: one has on-chip UTMI USB PHY (there is internal PLL with 60MHz output), while the other does not have.

- (3) APM32F4xxRxT6 series don't support EMMC module.

- (4) For product information of each model, refer to the datasheet.

### 2.3 Memory mapping

The assigned addresses of memory mapping include the core (including core peripherals), on-chip Flash (including main memory area, system memory area and option bytes), on-chip SRAM, and bus peripherals (including AHB and APB peripherals). Please refer to the data manual of the corresponding model for specific information of various addresses.

#### 2.3.1 Embedded SRAM

The product has backup SRAM (4KB) and system SRAM (192KB). The system SRAM is divided into three parts: SRAM1 (112KB), SRAM2 (16KB) and CCM (64KB).

#### SRAM1 and SRAM2

The main SRAM1 and auxiliary SRAM2 can be accessed by byte, half word (16 bits) or full word (32 bits). The mapping address of SRAM1 and SRAM2 is 0x2000 0000, and the main module can be accessed by all AHB.

#### Core couple memory (CCM)

The mapping address of CCM (64KB) is 0x1000 0000, and it can only be accessed by CPU through D-bus.

#### 2.3.2 Bit band

Arm<sup>®</sup> Cortex<sup>®</sup>-M4F memory is mapped with two bit-band areas, and it maps each word in the alias memory area to one bit in the bit-band memory. Write a word to the alias memory and there will be the same effect as the read-changewrite operation on the target of the bit-band area. Both peripheral register and SRAM are mapped into a bit band area, and it is allowed to perform single bitband write and read operations.

The following gives a mapping formula:

bit\_word\_addr=bit\_band\_base+ (byte\_offset×32) + (bit\_number×4)

## 2.4 Startup configuration

APM32F4xx series MCU realizes a special mechanism. By configuring the BOOT[1:0] pin, there are three different startup modes, and the system can not only start from Flash memory or system memory, but also start from the built-in SRAM. The memory selected as the start zone is determined by the selected startup mode.

| Startup mode configuration |           | Startup mode                    | Access mode                                                                                                                                                                                       |

|----------------------------|-----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT1 pin                  | BOOT0 pin |                                 |                                                                                                                                                                                                   |

| х                          | 0         | Main flash<br>memory<br>(Flash) | The main flash memory is mapped to the boot<br>space, but it can still be accessed at its original<br>address, that is, the contents of the flash memory<br>can be accessed in two address areas. |

| 0                          | 1         | System<br>memory                | The system memory is mapped to the boot space<br>(0x0000 0000), but it can still be accessed at its<br>original address.                                                                          |

| 1                          | 1         | Built-in SRAM                   | SRAM can be accessed only at the starting address.                                                                                                                                                |

#### Table 6 Startup Mode Configuration and Access Mode

Note:

- (1) The boot space address is 0x0000 0000

- (2) The original address of Flash is 0x0800 0000

- (3) The original address of the system memory is 0x1FFF 0000

- (4) The starting address of SRAM is 0x2000 0000

- (5) The user can select the startup mode after reset by setting the state of BOOT[1:0] pin.

- (6) BOOT pin should keep the user's required startup configuration in standby mode. When exiting from the standby mode, the value of boot pin will be latched.

- (7) If you choose to start from built-in SRAM, you must use NVIC's exception table and offset register to remap the vector table to SRAM when writing the application code.

#### **Physical remapping**

After BOOT pin is selected, MMSEL bit of SYSCFG\_MMSEL register can be modified through software program to configure some register to allow access from I-Code bus. See SYSCFG register for specific configuration.

#### Embedded BootLoader

The embedded BootLoader mode will be selected to reprogram Flash through

which of the following serial port:

- USART1

- USART3

- CAN2

- USB OTG\_FS slave mode

## 3 FLASH memory

## 3.1 Full name and abbreviation description of terms

| Full name in English    | English abbreviation |

|-------------------------|----------------------|

| Flash Memory Controller | FMC                  |

| One-time Programmable   | OTP                  |

| Adaptive Real-time      | ART                  |

Table 7 Full name and abbreviation description of terms

### 3.2 Introduction

This chapter mainly introduces the storage structure, read, erase, write, read/write protection, unlock/lock characteristics of Flash, and the involved register functional description.

## 3.3 Main characteristics

- (1) Flash memory structure

- Contain main memory area and information block

- The capacity of main memory area is up to 1MB

- The information block is divided into system memory, OTP area and option byte three areas

- The capacity of the system memory area is 30KB, for storing BootLoader program, 96-bit unique UID, and main memory area capacity information

- The OTP area is 528Bytes, 512 OTP bytes are used for storing user data, and the remaining 16 bytes are used for locking the corresponding OTP data block

- The capacity of the option byte area is 16Bytes

- (2) Functional Description

- Operate the Flash:

- Read

- Sector/Mass Erase

- Write

- Read/Write protection

- Operate the option byte:

- Read

- Erase

- Write

- Read/Write protection

## 3.4 Flash memory structure

| Block       | Name             | Address range             | Size (byte) | Sector    |

|-------------|------------------|---------------------------|-------------|-----------|

|             |                  | 0x0800 0000–0x0800 3FFF   |             | Sector 0  |

|             |                  | 0x0800 4000–0x0800 7FFF   | 16K         | Sector 1  |

|             |                  | 0x0800 8000–0x0800 BFFF   | 16K         | Sector 2  |

|             |                  | 0x0800 C000-0x0800 FFFF   | 16K         | Sector 3  |

| Main me     | emory block      | 0x0801 0000 – 0x0801 FFFF | 64K         | Sector 4  |

|             |                  | 0x0802 0000 – 0x0803 FFFF | 128K        | Sector 5  |

|             |                  |                           |             |           |

|             |                  | 0x080E 0000-0x080F FFFF   | 128K        | Sector 11 |

| Information | System<br>memory | 0x1FFF 0000–0x1FFF 77FF   | 30K         | -         |

| block       | OTP area         | 0x1FFF 7800–0x1FFF 7A0F   | 528         | -         |

|             | Option byte      | 0x1FFF C000-0x1FFF C00F   | 16          | -         |

#### Table 8 Flash Memory Structure

Note: The number of sectors included by the main memory block of APM32F405/415xG

APM32F407/417xExG series products is related to the capacity of specific Flash; see the Data Manual for the capacity of Flash of different models.

## 3.5 Flash memroy functional description

#### 3.5.1 Read Flash

Flash has a prefetch buffer area, and it can be turned on only when the power supply voltage is not lower than 2.1V.

The reading speed of Flash is affected by the number of wait cycles, and the number of wait cycles is affected by HCLK and power supply voltage. Assuming the wait cycle is n, and the rising base of HCLK range is X

- When (n+1) X is less than the maximum value: nX<HCLK≤ (n+1) X</li>

- When (n-1) X is greater than the maximum value: nX<HCLK≤ maximum value</li>

| Voltage range | 1.8V-2.1V | 2.1V-2.4V | 4V 2.4V-2.7V 2.7V |        |  |

|---------------|-----------|-----------|-------------------|--------|--|

| Х             | 20MHz     | 22MHz     | 24MHz             | 30MHz  |  |

| Maximum value | 160MHz    | 168MHz    | 168MHz            | 168MHz |  |

#### Table 9 X Affected by Voltage Range and Maximum Value of HCLK

Note:

When PMU\_CTRL register VOSSEL=0, the maximum value of HCLK is 144MHz; when VOSSEL=1, the maximum value of HCLK is 168MHz.

CPU frequency can be adjusted by selecting different wait cycles, so as to adjust the reading speed of Flash.

#### 3.5.1.1 Adaptive real-time memory accelerator (ART)

ART accelerator can improve the execution speed of Flash, so that the Flash can execute programs with fewer wait cycles at high CPU frequency.

#### Prefetch buffer area

When needing to insert wait cycle to access Flash, the next instruction line of Flash can be pre-read through I-Code bus, to improve the access rate.

#### I-cache

I-cache is an instruction buffer memory. The instructions in I-cache can be obtained without delay. The system can store 64 lines of 128-bit instructions in I-cache and the I-cache function can be enabled through ICACHEEN bit of FMC\_ACCTRL register.

#### **D**-cache

D-cache is a data buffer memory. The system accesses the data buffer area of Flash through D-Bus to reduce the waiting time. Access of D-bus is prior to I-bus. The system can store 8 lines of 128-bit instructions in D-cache and the D-cache function can be enabled through DCACHEEN bit of FMC\_ACCTRL register.

#### 3.5.2 Main memory block

When erasing/writing to the main memory, Flash can no longer be read.

#### Number of parallel bits

The number of parallel bits is the number of bytes to be processed when erasing/writing to the Flash, and it is determined by the power supply voltage and the use of external power supply. The number of parallel bits is configured by programming the PGSIZE bit of FMC\_CTRL register. The determinant factors and the number of parallel bits are shown in the table below:

| Table To Relationship between Determinant'i actors and Namber of Falaner Dits |         |         |         |         |                                |  |  |

|-------------------------------------------------------------------------------|---------|---------|---------|---------|--------------------------------|--|--|

| Voltage range (V)                                                             | 1.8-2.1 | 2.1-2.4 | 2.4-2.7 | 2.7-3.6 | 2.7-3.6 (external VPP is used) |  |  |

| Number of parallel                                                            | 8-bit   | 16-bit  |         | 32-bit  | 64-bit                         |  |  |

#### Table 10 Relationship between Determinant Factors and Number of Parallel Bits

#### 3.5.2.1 Erase main memory block

Flash can support sector erase and mass erase (erase all). Mass erase does not affect OTP sector or configuration sector.

#### Main memory page erase

Page erase is an independent erase according to the main memory area page selected by the program, which will not have any impact on the page not selected for erasure.

After the correct page erase (or flash write operation) is completed, OPRCMP bit of FMC\_STS register will be set. If OPCINTEN interrupt is enabled, an operation completion interrupt will be triggered. Users need to note that the page to be erased must be a valid page (the valid address of the main memory area and the address not protected by write).

#### Main memory mass erase

The mass erase operation will erase all the contents in the main storage area of Flash, so the users need to pay special attention when using it to avoid the loss of important data caused by misoperation.

Mass erase does not affect OTP sector or configuration sector.

#### 3.5.2.2 Write main memory block

Flash supports byte, half-word, word, and double-word write operation, specifically depending on the number of parallel bits.

#### It's important to check whether the destination address has been erased before writing to ensure correct writing. Flash unit must be earsed into 1 before writing.

If the destination address has write protection, the written data is invalid and a write protection error will be triggered (WPROTERR bit of FMC\_STS register is set to "1").

In FMC\_STS register, there are three write error bits, which are PGALGERR (programming alignment error), PGPRLERR (programming parallelism error) and PGSEQERR (programming sequence error).

#### Programming alignment error

To program more than 128-bit lines of data to the Flash, a programming alignment error will occur, and the PGALGERR bit will be set to 1.

#### Programming parallelism error

If the width of the write operation is inconsistent with the number of parallel bits,

the write operation will be suspended, a programming parallelism error will be generated, and the PGPRLERR bit will be set to 1.

#### Programming sequence error

The correct programming sequence is:

- (1) Confirm the operation currently not performed to the Flash through FMC\_STS[BUSY]

- (2) Set FMC\_CTRL[PG] to 1

- (3) Conduct write operation

- (4) Operation is completed, waiting for BUSY bit to be cleared to zero

If the programming sequence is wrong, a programming sequence error will occur, and the PGSEQERR bit will be set to 1.

#### 3.5.2.3 Lock/unlock

FMC\_CTRL[LOCK] can only be set to 1, so as to lock Flash control register, and the main memory block area can not be programed.

Write the keywords 0x4567 0123 and 0xCDEF 89AB to the FMC\_KEY register, and when the system detects unlocking sequence, it will clear the LOCK bit of FMC\_CTRL register to zero, Flash control register and the main memory block will be unlocked.

#### 3.5.2.4 Buffer

If the write operation of Flash involves some data in D-cache, the data in Flash and D-cache will be modified.

If the erase operation of Flash involves the data in D-cache or I-cache, the data shall be written to the cache before it.

#### 3.5.2.5 Interrupt

An interrupt will occur in case of any of the following events:

- End of operation: End of erase/write operation

- Write protection error: Perform erase/write operation for the write protection area

- Programming error: An error occurs during erase/write/read

When OPCINTEN bit or ERRINTEN bit in FMC\_CTRL register is set to 1 and the corresponding interrupt event occurs, an interrupt will be generated.

#### 3.5.3 **Option byte**

The address and composition of the option byte are shown in the following table, and the specific meaning description can be seen in the corresponding bit of FMC\_OPTCTRL register.

| Address     | Bit field | Option byte | Functional description                      |

|-------------|-----------|-------------|---------------------------------------------|

|             | 1:0       | -           | -                                           |

|             | 3:2       | BORLVL      | Brownout reset level                        |

|             | 4         | -           | -                                           |

| 0x1FFF C000 | 5         | WDTSEL      | Select the watchdog                         |

|             | 6         | RSTSTOP     | Reset occurs when entering the stop mode    |

|             | 7         | RSTSTDB     | Reset occurs when entering the standby mode |

|             | 15:8      | RPROT       | Read protection                             |

| 0x1FFF C008 | 11:0      | NWPROT      | No write protection                         |

|             | 15:12     | -           | -                                           |

Table 11 Instructions for Option Bytes

#### 3.5.3.1 Erase/write option byte

The option byte must be unlocked before erasing/writing.

The programming sequence of option byte is:

- (1) Confirm the operation currently not performed to the Flash through FMC\_STS[BUSY]

- (2) Write the programming value to FMC\_OPTCTRL

- (3) Set FMC\_OPTCTRL[OPTSTART] to 1

- (4) Operation is completed, waiting for BUSY bit to be cleared to zero

#### Note:

If the page erase/write operation of the main memory block is performed immediately after the option byte write operation is completed, the following steps must be performed after the option byte write operation is completed:

①Unlock the main memory block

2)Write 0x08 in the address: 0x40023C30

③Lock the main memory block

After the above three steps are performed, the page erase/write operation of the main memory block could be performed.

#### 3.5.3.2 Lock/unlock

FMC\_OPTCTRL[OPTLOCK] can only be set to 1, so as to lock the option byte area.

Write the keywords 0x0819 2A3B and 0x4C5D 6E7F to the FMC\_OPTKEY register, and when the system detects unlocking sequence, it will clear the OPTLOCK bit of FMC\_OPTCTRL register to zero and the option byte will be unlocked.

#### 3.5.4 Write protection

In order to prevent accidental rewriting of Flash due to program disorder, in default state, the Flash supports write protection function of up to 12 user sectors; when the corresponding bit of the FMC\_OPTCTRL[NWPROT] bit field is at low level, the corresponding sector will be write-protected, and the sector cannot be erased/written.

#### 3.5.4.1 Write protection error

FMC\_STS[WPROTERR] is a write protection error bit, and it will be set to 1 when any of the following events occurs:

- Perform erase/write operation for the write protection area

- Execute page erase/mass erase for invalid sector

- Meanwhile, select page erase and mass erase

- Flash is under read protection but detects erase/write request

- Perform write operation for user configuration area

- Perform write operation for the locked OTP area

#### 3.5.5 Read protection

In order to prevent untrusted code from reading Flash data, you can choose to use the read protection function for the Flash and the read protection level can be selected by configuring the value of the FMC\_OPTCTRL[RPROT] bit field. The read protection has three levels, namely, Level 0, Level 1 and Level 2.

The access restriction at different read protection levels is shown in the following table.

|                       |         |       | Bootstrap from |               | Debuggng function, bootstrap from RAM or |  |              |  |

|-----------------------|---------|-------|----------------|---------------|------------------------------------------|--|--------------|--|

| Storage               | Level   | Flash |                | system memory |                                          |  |              |  |

| area                  |         | Read  | Write          | Erase         | Read Write                               |  | Erase        |  |

| OTP                   | Level 1 | ✓ -   |                |               |                                          |  |              |  |

| OIF                   | Level 2 |       |                | -             | ×                                        |  | -            |  |

| Option                | Level 1 |       | $\checkmark$   |               |                                          |  |              |  |

| byte                  | Level 2 |       | ×              |               |                                          |  |              |  |

| Flash                 | Level 1 |       |                |               | <b>X X</b> (1)                           |  | <b>X</b> (1) |  |

| and<br>backup<br>SRAM | Level 2 |       | $\checkmark$   |               | X                                        |  |              |  |

Table 12 Restriction at Different Read Levels

Note:

(1) means that only when Level 1 changes to Level 0, can the data of Flash and backup SRAM be erased.

"√" means the operation is allowed, "X" means not allowed, and "-" means undefined.

#### 3.5.5.1 Level 0

When FMC\_OPTCTRL[RPROT]=0xAA, the read protection function is not used for Flash.

#### 3.5.5.2 Level 1

When FMC\_OPTCTRL[RPROT]=any value (except 0xAA and 0xCC), the read protection level is 1. At this time, if the level is adjusted to Level 0, mass erase operation will be performed to erase all data of Flash and backup SRAM. Mass erase only affects user code area, and write-protected other option bytes and OTP will not be affected.

#### 3.5.5.3 Level 2

When FMC\_OPTCTRL[RPROT]=0xCC, the read protection level is 2. Then:

- Reserve the read protection function of Level 1

- It is not allowed to bootstrap from RAM or system memory

- JTAG, SWV, ETM and boundary scan is disabled

- The option byte is locked

Note: When the read protection level is set to 2, it cannot be degraded any more.

#### 3.5.6 **OTP**

The following table shows OTP structure.

| Table 13 OTP Structure |        |         |         |          |          |  |  |

|------------------------|--------|---------|---------|----------|----------|--|--|

| Address                | [31:0] | [63:32] | [95:64] | [127:96] | Block    |  |  |

| 0x1FFF 7800            | OTP0   | OTP0    | OTP0    | OTP0     | Data     |  |  |

| 0x1FFF 7810            | OTP0   | OTP0    | OTP0    | OTP0     | block 0  |  |  |

| 0x1FFF 7820            | OTP1   | OTP1    | OTP1    | OTP1     | Data     |  |  |

| 0x1FFF 7830            | OTP1   | OTP1    | OTP1    | OTP1     | block 1  |  |  |

| 0x1FFF 7840            | OTP2   | OTP2    | OTP2    | OTP2     | Data     |  |  |

| 0x1FFF 7850            | OTP2   | OTP2    | OTP2    | OTP2     | block 2  |  |  |

|                        |        |         |         |          |          |  |  |

| 0x1FFF 79E0            | OTP15  | OTP15   | OTP15   | OTP15    | Data     |  |  |

| 0x1FFF 79F0            | OTP15  | OTP15   | OTP15   | OTP15    | block 15 |  |  |

| Address     | [31:0] | [63:32] | [95:64] | [127:96] | Block |

|-------------|--------|---------|---------|----------|-------|

| 0x1FFF 7A00 | LOCKB0 | LOCKB4  | LOCKB8  | LOCKB12  | Lock  |

|             |        |         |         |          | block |

|             | LOCKB3 | LOCKB7  | LOCKB11 | LOCKB15  | DIOCK |

OTP consists of 16 32-byte data blocks and 1 16-byte lock block. The lock block n is used to lock the data block n (n=0...15), and the corresponding data block can be programmed only when the value of the lock block is 0x00. The value of the lock block can only be 0x00 or 0xFF; otherwise, the OTP byte cannot be used normally.

Note that neither data block nor lock block of OTP can be erased.

## 3.6 Register address mapping

| Register name | Description                   | Offset address |

|---------------|-------------------------------|----------------|

| FMC_ACCTRL    | Flash access control register | 0x00           |

| FMC_KEY       | Flash key register            | 0x04           |

| FMC_OPTKEY    | Flash option key register     | 0x08           |

| FMC_STS       | Flash state register          | 0x0C           |

| FMC_CTRL      | Flash control register        | 0x10           |

| FMC_OPTCTRL   | Flash option control register | 0x14           |

#### Table 14 FMC Register Address Mapping

## 3.7 Register functional description

## 3.7.1 Flash access control register (FMC\_ACCTRL)

Offset address: 0x00

Reset value: 0x0000 0000

| Field | Name     | R/W | Description                                                                                                                              |  |  |

|-------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2:0   | WAITP    | R/W | Wait Period<br>This bit means the number of wait cycles.<br>000: 0<br>001: 1<br>010: 2<br>011: 3<br>100: 4<br>101: 5<br>110: 6<br>111: 7 |  |  |

| 7:3   | Reserved |     |                                                                                                                                          |  |  |

| Field | Name      | R/W | Description              |  |

|-------|-----------|-----|--------------------------|--|

|       |           |     | Prefetch Enable          |  |

| 8     | PREFEN    | R/W | 0: Disable               |  |

|       |           |     | 1: Enable                |  |

|       |           |     | Instruction Cache Enable |  |

| 9     | ICACHEEN  | R/W | 0: Disable               |  |

|       |           |     | 1: Enable                |  |

|       |           |     | Data Cache Enable        |  |

| 10    | DCACHEEN  | R/W | 0: Disable               |  |

|       |           |     | 1: Enable                |  |

|       |           |     | Instruction Cache Reset  |  |

| 11    | ICACHERST | W   | 0: Invalid               |  |

|       |           |     | 1: Reset                 |  |

|       |           |     | Data Cache Reset         |  |

| 12    | DCACHERST | R/W | 0: Invalid               |  |

|       |           |     | 1: Reset                 |  |

| 31:13 | Reserved  |     |                          |  |

#### 3.7.2 Flash key register (FMC\_KEY)

Offset address: 0x04

Reset value: 0x0000 0000

| Field | Name | R/W | Description                                                             |

|-------|------|-----|-------------------------------------------------------------------------|

| 31:0  | KEY  | W   | Key<br>When unlocking, this key needs to be written into this register. |

## 3.7.3 Flash option key register (FMC\_OPTKEY) Offset address: 0x08

#### Reset value: 0x0000 0000

| Field | Name   | R/W | Description                                                                    |

|-------|--------|-----|--------------------------------------------------------------------------------|

| 31:0  | OPTKEY | W   | Option Key<br>When unlocking, this key needs to be written into this register. |

## 3.7.4 Flash state register (FMC\_STS)

Offset address: 0x0C

Reset value: 0x0000 0000

| Field | Name     | R/W   | Description                                                                                   |  |  |

|-------|----------|-------|-----------------------------------------------------------------------------------------------|--|--|

| 0     | OPRCMP   | RC_W1 | Operation Complete<br>This bit will be set to 1 when the operation for Flash is<br>completed. |  |  |

| 1     | OPRERR   | RC_W1 | Operation Error<br>This bit will be set to 1 when an error occurs in operation<br>process.    |  |  |

| 3:2   | Reserved |       |                                                                                               |  |  |

| Field | Name     | R/W   | Description                                                                                                                    |  |  |  |

|-------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4     | WPROTERR | RC_W1 | Write Protection Error<br>This bit will be set to 1 when erse/write operation is performed<br>for Flash write protection area. |  |  |  |

| 5     | PGALGERR | RC_W1 | Programming Alignment Error<br>This bit will be set to 1 when a programming alignment error<br>occurs.                         |  |  |  |

| 6     | PGPRLERR | RC_W1 | Programming Parallelism Error<br>This bit will be set to 1 when a programming parallelism error<br>occurs.                     |  |  |  |

| 7     | PGSEQERR | RC_W1 | Programming Sequence Error<br>This bit will be set to 1 when a programming sequence error<br>occurs.                           |  |  |  |

| 15:8  | Reserved |       |                                                                                                                                |  |  |  |

| 16    | BUSY     | R     | Busy<br>This bit will be set to 1 when operation is performed for Flash.                                                       |  |  |  |

| 31:17 | Reserved |       |                                                                                                                                |  |  |  |

#### 3.7.5 Flash control register (FMC\_CTRL)

Offset address: 0x10

Reset value: 0x8000 0000

This register can be accessed only when there is no Flash operation ongoing.

| Field | Name     | R/W                                                                                                                                             | Description                                                                                                                                                              |  |  |  |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | PG       | R/W                                                                                                                                             | Programming<br>When this bit is set to 1, Flash programming can be enabled.                                                                                              |  |  |  |

| 1     | SERS     | R/W                                                                                                                                             | Sector Erase<br>When this bit is set to 1, sector erase can be enabled.                                                                                                  |  |  |  |

| 2     | MERS     | R/W                                                                                                                                             | Mass Erase<br>When this bit is set to 1, mass erase can be enabled.                                                                                                      |  |  |  |

| 6:3   | SNUM     | R/W                                                                                                                                             | Sector Number<br>This bit field is used for the specified erase sector.<br>0000: Sector 0<br>0001: Sector 1<br>0010: Sector 2<br><br>1011: Sector 11<br>Others: Reserved |  |  |  |

| 7     | Reserved |                                                                                                                                                 |                                                                                                                                                                          |  |  |  |

| 9:8   | PGSIZE   | PGSIZE R/W Program Size<br>This bit field is used to select the number of parallel bits.<br>00: 8-bit<br>01: 16-bit<br>10: 32-bit<br>11: 64-bit |                                                                                                                                                                          |  |  |  |

| 15:10 | Reserved |                                                                                                                                                 |                                                                                                                                                                          |  |  |  |

| Field | Name     | R/W Description |                                                                                                                                                                      |  |  |  |

|-------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 16    | START    | R/S             | Start<br>When this bit is set to 1, the erase operation can be started. This bit<br>will be cleared to zero when BUSY bit is cleared to zero.                        |  |  |  |

| 23:17 |          |                 | Reserved                                                                                                                                                             |  |  |  |

| 24    | OPCINTEN | R/W             | Operation Complete Interrupt Enable<br>0: Disable<br>1: Enable                                                                                                       |  |  |  |

| 25    | ERRINTEN | R/W             | Error interrupt Enable<br>0: Disable<br>1: Enable                                                                                                                    |  |  |  |

| 30:26 | Reserved |                 |                                                                                                                                                                      |  |  |  |

| 31    | LOCK     | R/S             | Lock<br>When this bit is set to 1, it means that this register is locked; when<br>the unlocking sequence is detected, it will be cleared to zero by the<br>hardware. |  |  |  |

## 3.7.6 Flash option control register (FMC\_OPTCTRL)

Offset address: 0x14

Reset value: 0x0FFF AAED

This register can be accessed only when there is no Flash operation ongoing.

| Field | Name     | R/W | Description                                                                                                                                                                                                                                                                                                     |  |  |  |

|-------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | OPTLOCK  | R/S | Option Lock<br>When this bit is set to 1, it means that this register is locked;<br>when the unlocking sequence is detected, it will be cleared to<br>zero by the hardware.                                                                                                                                     |  |  |  |

| 1     | OPTSTART | R/S | Option Start<br>After this bit is set to 1 by the software, the option byte can be<br>operated and it can be cleared to zero when the BUSY bit is set<br>to zero.                                                                                                                                               |  |  |  |

| 3:2   | BORLVL   | R/W | Brownout Reset Level<br>When the power supply voltage is less than the threshold of the<br>brownout reset level, a reset will be generated.<br>00: Level 3, voltage range: 2.7V-3.6V<br>01: Level 2, voltage range: 2.4V-2.7V<br>10: Level 1, voltage range: 2.1V-2.4V<br>11: Disable, voltage range: 1.8V-2.1V |  |  |  |

| 4     | Reserved |     |                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 5     | WDTSEL   | R/W | Watchdog Select<br>0: Hardware watchdog<br>1: Software watchdog                                                                                                                                                                                                                                                 |  |  |  |

| 6     | RSTSTOP  | R/W | nReset in STOP Mode<br>0: Reset occurs when entering the Stop mode<br>1: Reset does not occur when entering the Stop mode                                                                                                                                                                                       |  |  |  |

| Field | Name     | R/W | Description                                                                                                                        |  |

|-------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------|--|

| 7     | RSTSTDB  | R/W | nReset in STANDBY Mode<br>0: Reset occurs when entering the Standby mode<br>1: Reset does not occur when entering the Standby mode |  |

| 15:8  | RPROT    | R/W | Read Protect<br>This bit field is used to select the eread protection level.<br>0xAA: Level 0<br>0xCC: Level 2<br>Others: Level 1  |  |

| 27:16 | NWPROT   | R/W | Not Write Protect<br>0: Write protection isenabled<br>1: Write protection is disabled                                              |  |

| 31:28 | Reserved |     |                                                                                                                                    |  |

## 4 External Memory Controller (EMMC)

## 4.1 Full name and abbreviation description of terms

| Full name in English                     | English<br>abbreviation |

|------------------------------------------|-------------------------|

| Static Random Access Memory              | SRAM                    |

| Read Only Memory                         | ROM                     |

| Pseudo Static Random Access Memory       | PSRAM                   |

| Random Access Memory                     | RAM                     |

| Synchronous Dynamic Random Access Memory | SDRAM                   |

| Multiplex                                | MUX                     |

| Width                                    | WID                     |

| Flash Memory                             | FM                      |

| Access                                   | ACC                     |

| Wait                                     | W                       |

| Signal                                   | S                       |

| Polarity                                 | POL                     |

| Asynchronous                             | ASYN                    |

| Burst                                    | BURST                   |

| Timing                                   | ТІМ                     |

| Setup                                    | SET                     |

| Hold                                     | HLD                     |

| Empty                                    | E                       |

| Table 15 Fu | ll name and | abbreviation | descrip | tion of terms |

|-------------|-------------|--------------|---------|---------------|

|             | ii name anu | appreviation | uescrip |               |

## 4.2 EMMC Overview

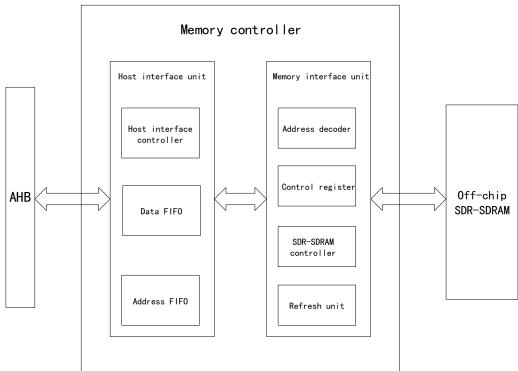

EMMC includes SMC (static memory controller) and DMC (dynamic memory controller). SMC is responsible for controlling SRAM, PSRAM, NandFlash, NorFlash and PCCard; DMC is responsible for controlling SDRAM.

## 4.3 SMC Introduction

SMC is used to manage the extended static memory peripherals; AHB transmission signals can be converted to the appropriate external devices; there are four internal memory blocks, each of which controls different types of

memory and is distinguished by chip selection signal; only one external device can be accessed at any moment; each memory block can be configured separately, and the timing can be programmed for external devices.

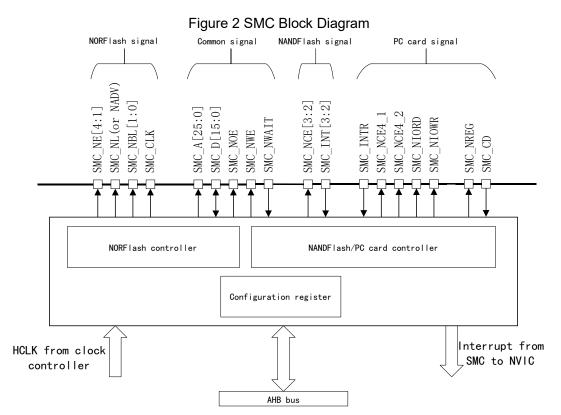

## 4.4 SMC Structure Block Diagram

SMC consists of five parts: AHB bus interface, configuration register, NORFlash controller, NANDFlash/PC card controller and external device interface, specifically as shown in the figure below:

## 4.5 SMC Functional Description

#### 4.5.1 SMC Access Rules

SMC is an interface for internal CPU to access external static memory through AHB bus. On AHB bus, the operation of 32-bit data will be converted into continuous 16 or 8-bit operation. In order to ensure the consistency of data transmission, SMC needs to comply with the following rules in external read-write operation:

- (1) When the width of AHB accessing external data is equal to that of memory data, the data can be transmitted normally without any problem.

- (2) When the width of AHB accessing external data is larger than that of memory data, the access operation will be automatically cut to be consistent with the width of external data for transmission.

(3) When the width of AHB accessing external data is less than that of memory data, if the external memory has the function of byte selection, it can transmit data normally through byte channel; if it does not have such function, it does not allow write operation, and only allows read operation.

#### 4.5.2 External device address mapping

SMC divides external devices into multiple memory blocks, and different memory blocks control different external devices. The specific classification is shown in the table below:

| Start address | End address | Memory block               | Memory type<br>supported |  |  |

|---------------|-------------|----------------------------|--------------------------|--|--|

| 0x60000000    | 0x6FFFFFFF  | Memory block 1<br>(4*64MB) | NOR/PSRAM                |  |  |

| 0x70000000    | 0x7FFFFFFF  | Memory block 2<br>(4*64MB) | NAND                     |  |  |

| 0x80000000    | 0x8FFFFFFF  | Memory block 3<br>(4*64MB) | NAND                     |  |  |

| 0x9000000     | 0x9FFFFFFF  | Memory block 4<br>(4*64MB) | PC card                  |  |  |

Table 16 External Device Address Mapping Table

#### 4.5.3 NOR flash memory and PSRAM

#### 4.5.3.1 Address mapping

Memory block 1 is used to control NOR/PSRAM memory, which is divided into four 64MB areas of the same size. The selection of each area depends on the value of HADDR [27:26], and the specific information is as follows:

| ······································ |                                |            |              |  |  |

|----------------------------------------|--------------------------------|------------|--------------|--|--|

| HADDR[27:26]                           | Start address End address      |            | Area block   |  |  |

| 00                                     | 0x60000000 0x63FFFFF Area blo  |            | Area block 1 |  |  |

| 01                                     | 0x64000000 0x67FFFFF Area bloc |            | Area block 2 |  |  |

| 10                                     | 0x68000000                     | 0x6BFFFFFF | Area block 3 |  |  |

| 11                                     | 0x6C000000                     | 0x6FFFFFFF | Area block 4 |  |  |

| Table 17 Address | Mapping | of Memory  | / Block 1 |

|------------------|---------|------------|-----------|

|                  | mapping | or mornory |           |

HADDR is the internal AHB address line that needs to be converted to the external memory. It is a byte address. However, some external memories are not accessed by byte, so the address may be inconsistent. In order to avoid the error caused by this situation, SMC will be adjusted according to the following rules:

- When the width of external memory data is 8 bits, HADDR[25:0] is connected to SMC\_A [25:0], while SMC\_A[25:0] is connected to the external memory address line.

- When the width of external memory data is 16 bits, HADDR[25:1] is connected to SMC\_A [24:0], while SMC\_A[24:0] is connected to the external memory address line.

#### 4.5.3.2 Interface signal and controller