# **User Manual**

# APM32F051x6x8

Arm® Cortex® -M0+ based 32-bit MCU

Version: V1.5

| 1   | Introduction and Document Description Rules     | 8  |

|-----|-------------------------------------------------|----|

| 1.1 | Introduction                                    | 8  |

| 1.2 | Document Description Rules                      | 8  |

| 2   | System Architecture                             | 11 |

| 2.1 | Full Name and Abbreviation Description of Terms | 11 |

| 2.2 | System Architecture Block Diagram               | 11 |

| 2.3 | Memory Mapping                                  | 12 |

| 2.4 | Startup Configuration                           | 13 |

| 3   | FLASH Memory ······                             | 15 |

| 3.1 | Full Name and Abbreviation Description of Terms | 15 |

| 3.2 | Main Characteristics                            | 15 |

| 3.3 | Flash Memory Structure                          | 15 |

| 3.4 | Functional Description                          | 16 |

| 3.5 | Register Address Mapping                        | 20 |

| 3.6 | Register Functional Description                 | 20 |

| 4   | System Configuration Controller (SYSCFG)        | 24 |

| 4.1 | Full Name and Abbreviation Description of Terms | 24 |

| 4.2 | Register Address Mapping                        | 24 |

| 4.3 | Register Functional Description                 | 24 |

| 5   | Reset and Clock Management (RCM)                | 30 |

| 5.1 | Full Name and Abbreviation Description of Terms | 30 |

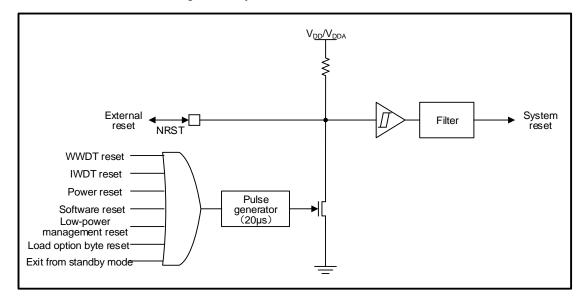

| 5.2 | Reset Functional Description                    | 30 |

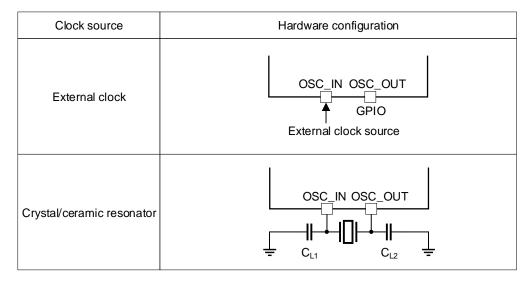

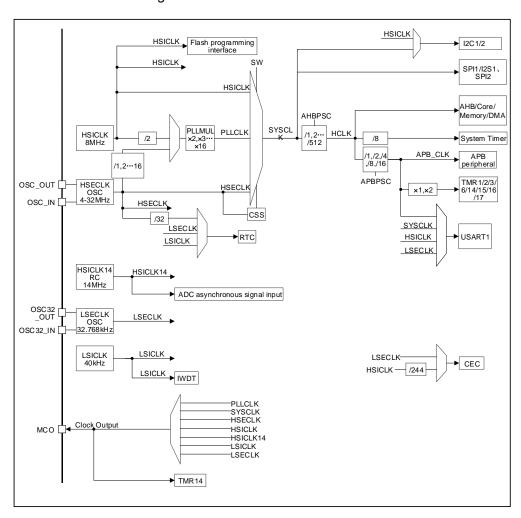

| 5.3 | Clock Control                                   | 32 |

| 5.4 | Register Address Mapping                        | 38 |

| 5.5 | Register Functional Description                 | 38 |

| 6   | Power Management Unit (PMU)                     | 54 |

| 6.1 | Introduction                                    | 54 |

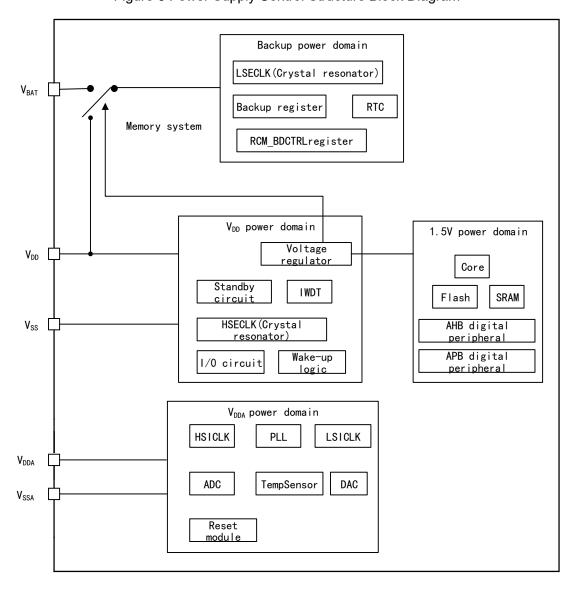

| 6.2 | Structure Block Diagram                         | 54 |

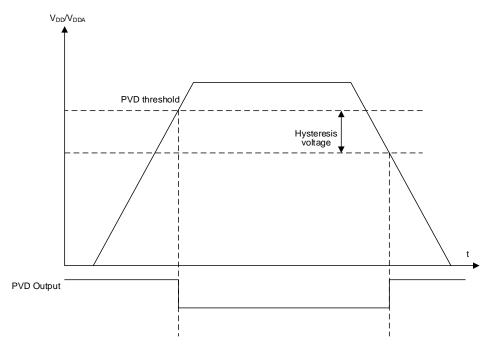

| 6.3 | Functional Description                          | 55 |

| 6.4 | Register Address Mapping                        | 59 |

| 6.5 | Register Functional Description                 | 59 |

| 7   | Nested Vector Interrupt Controller (NVIC)       | 62 |

| 7.1 | Full Name and Abbreviation Description of Terms | 62 |

| 7.2 | Introduction                                    | 62 |

| 7.3 | Main Characteristics                            | 62 |

| 7.4 | Interrupt and Exception Vector Table            | 62 |

| 8   | External Interrupt and Event Controller (EINT)  | 64 |

| 8.1  | Introduction                                            | 64         |

|------|---------------------------------------------------------|------------|

| 8.2  | Main Characteristics                                    | 64         |

| 8.3  | Functional Description                                  | 64         |

| 8.4  | Register Address Mapping                                | 66         |

| 8.5  | Register Functional Description                         | 66         |

| 9    | Direct Memory Access (DMA)                              | ····· 70   |

| 9.1  | Full Name and Abbreviation Description of Terms         | 70         |

| 9.2  | Introduction                                            | 70         |

| 9.3  | Main Characteristics                                    | 70         |

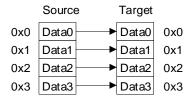

| 9.4  | Functional Description                                  | 71         |

| 9.5  | Register Address Mapping                                | 76         |

| 9.6  | Register Functional Description                         | 76         |

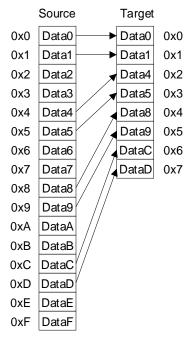

| 10   | Debug MCU (DBGMCU)······                                | 80         |

| 10.1 | Full Name and Abbreviation Description of Terms         | 80         |

| 10.2 | Introduction                                            | 80         |

| 10.3 | Main Characteristics                                    | 80         |

| 10.4 | Functional Description                                  | 81         |

| 10.5 | Register Address Mapping                                | 81         |

| 10.6 | Register Functional Description                         | 81         |

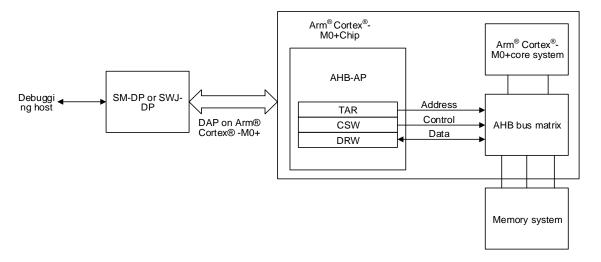

| 11   | General-purpose/Alternate Function Input/Output Pin (GP | IO/AFIO)85 |

| 11.1 | Full Name and Abbreviation Description of Terms         | 85         |

| 11.2 | Main Characteristics                                    | 85         |

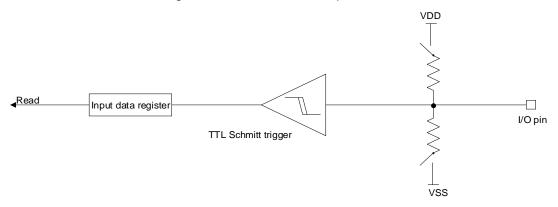

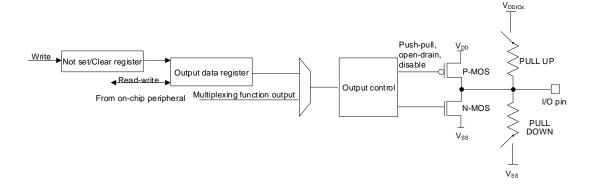

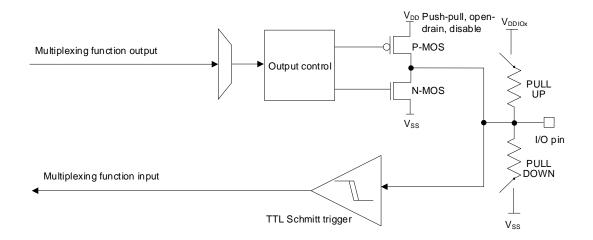

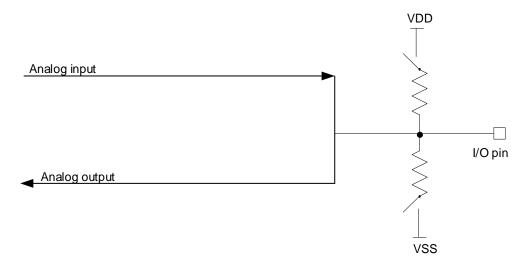

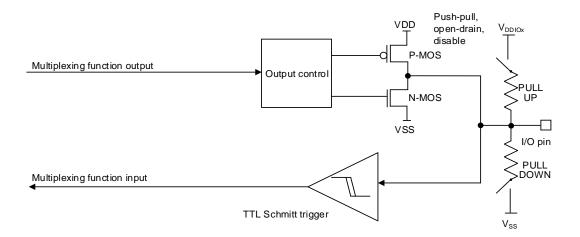

| 11.3 | Structure Block Diagram                                 | 86         |

| 11.4 | Functional Description                                  | 86         |

| 11.5 | Register Address Mapping                                | 92         |

| 11.6 | Register Functional Description                         | 92         |

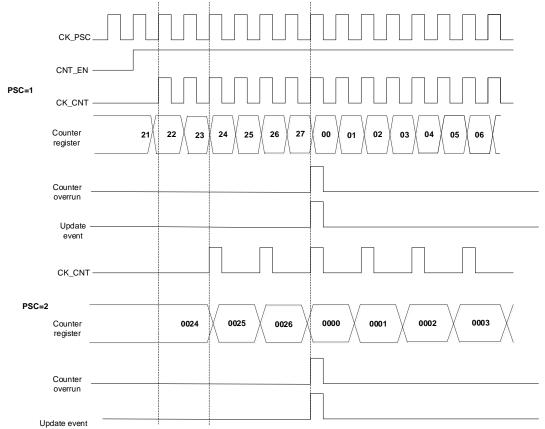

| 12   | Timer Overview                                          | 98         |

| 12.1 | Full Name and Abbreviation Description of Terms         | 98         |

| 12.2 | Timer Category and Main Difference                      | 98         |

| 13   | Basic Timer (TMR6) ······                               | 101        |

| 13.1 | Introduction                                            | 101        |

| 13.2 | Main Characteristics                                    | 101        |

| 13.3 | Structure Block Diagram                                 | 101        |

| 13.4 | Functional Description                                  | 101        |

| 13.5 | Register Address Mapping                                | 103        |

| 13.6 | Register Functional Description                         | 103        |

| 14   | General-purpose Timer (TMR2/TMR3) ······                | 106        |

| 14.1 | Introduction                                    | 106 |

|------|-------------------------------------------------|-----|

| 14.2 | Main Characteristics                            | 106 |

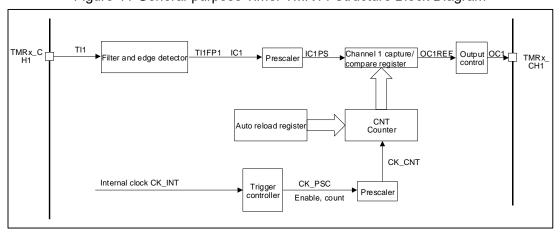

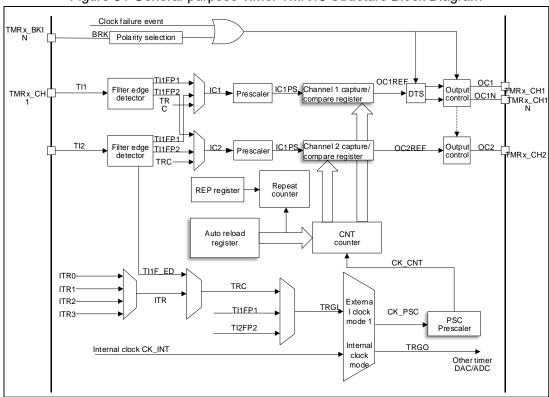

| 14.3 | Structure Block Diagram                         | 107 |

| 14.4 | Functional Description                          | 107 |

| 14.5 | Register Address Mapping                        | 119 |

| 14.6 | Register Functional Description                 | 120 |

| 15   | General-purpose Timer (TMR14)                   | 136 |

| 15.1 | Introduction                                    | 136 |

| 15.2 | Main Characteristics                            | 136 |

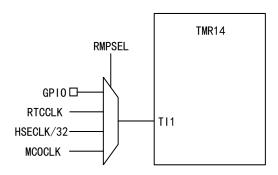

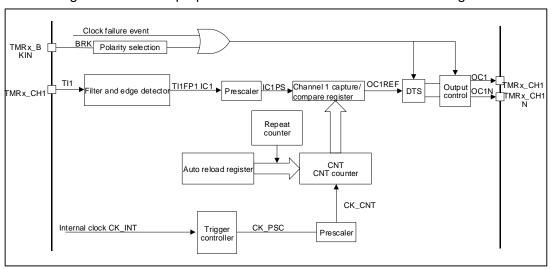

| 15.3 | TMR1 Structure Block Diagram                    | 136 |

| 15.4 | TMR14 Functional Description                    | 137 |

| 15.5 | Register Address Mapping                        | 144 |

| 15.6 | Register Functional Description                 | 144 |

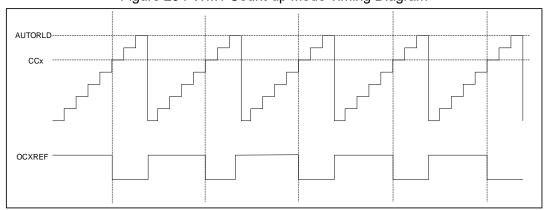

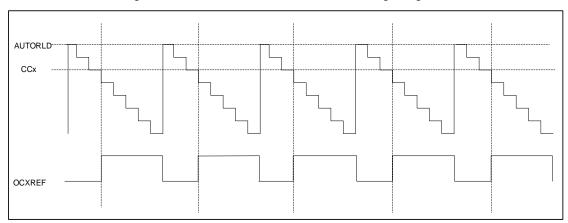

| 16   | General-purpose Timer (TMR15/16/17) ·····       | 151 |

| 16.1 | Introduction                                    | 151 |

| 16.2 | Main Characteristics                            | 151 |

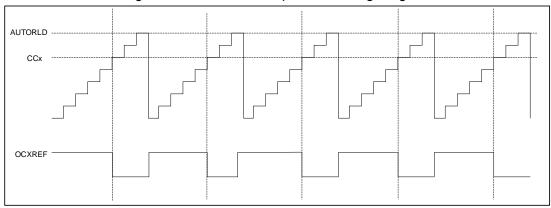

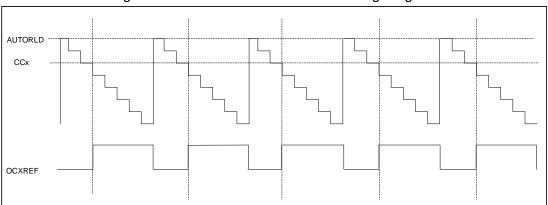

| 16.3 | Structure Block Diagram                         | 152 |

| 16.4 | Functional Description                          | 153 |

| 16.5 | TMR15 register Address Mapping                  | 164 |

| 16.6 | TMR15 Register Functional Description           | 164 |

| 16.7 | TMR16 and TMR17 Register Address Mapping        | 177 |

| 16.8 | TMR16 and TMR17 Register Functional Description | 178 |

| 17   | Advanced Timer (TMR1)                           | 189 |

| 17.1 | Introduction                                    | 189 |

| 17.2 | Main Characteristics                            | 189 |

| 17.3 | Structure Block Diagram                         | 190 |

| 17.4 | Functional Description                          | 190 |

| 17.5 | Register Address Mapping                        | 206 |

| 17.6 | Register Functional Description                 | 207 |

| 18   | Watchdog Timer (WDT) ······                     | 225 |

| 18.1 | Introduction                                    | 225 |

| 18.2 | Independent Watchdog                            | 225 |

| 18.3 | Window Watchdog                                 | 227 |

| 18.4 | IWDT Register Address Mapping                   | 228 |

| 18.5 | IWDT Register Functional Description            | 229 |

| 18.6 | WWDT Register Address Mapping                   | 231 |

| 18.7 | WWDT Register Functional Description            | 231 |

| 19   | Real-time Clock (RTC)                                         | 233  |

|------|---------------------------------------------------------------|------|

| 19.1 | Full Name and Abbreviation Description of Terms               | 233  |

| 19.2 | Introduction                                                  | 233  |

| 19.3 | Main Characteristics                                          | 233  |

| 19.4 | Structure Block Diagram                                       | 234  |

| 19.5 | Functional Description                                        | 234  |

| 19.6 | Register Address Mapping                                      | 240  |

| 19.7 | Register Functional Description                               | 240  |

| 20   | Universal Synchronous/Asynchronous Transceiver (USART         | )252 |

| 20.1 | Full Name and Abbreviation Description of Terms               | 252  |

| 20.2 | Introduction                                                  | 252  |

| 20.3 | Main Characteristics                                          | 252  |

| 20.4 | Functional Description                                        | 254  |

| 20.5 | Register Address Mapping                                      | 270  |

| 20.6 | Register Functional Description                               | 270  |

| 21   | Internal Integrated Circuit Interface (I2C)                   | 283  |

| 21.1 | Full Name and Abbreviation Description of Terms               | 283  |

| 21.2 | Introduction                                                  | 283  |

| 21.3 | Main Characteristics                                          | 283  |

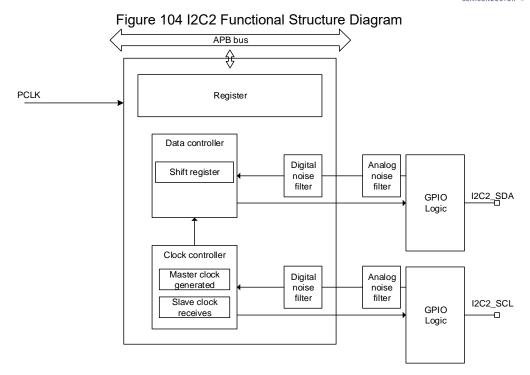

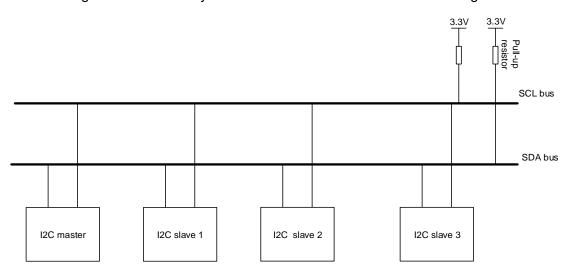

| 21.4 | Structure Block Diagram                                       | 285  |

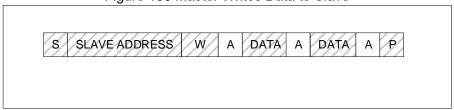

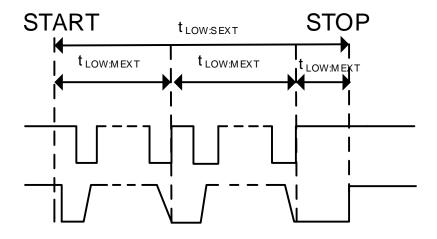

| 21.5 | Functional Description                                        | 286  |

| 21.6 | Register Address Mapping                                      | 296  |

| 21.7 | Register Functional Description                               | 297  |

| 22   | Serial Peripheral Interface/On-chip Audio Interface (SPI/I2S) | 308  |

| 22.1 | Full Name and Abbreviation Description of Terms               | 308  |

| 22.2 | Introduction                                                  | 308  |

| 22.3 | Main Characteristics of SPI                                   | 309  |

| 22.4 | Main Characteristics of I2S                                   | 309  |

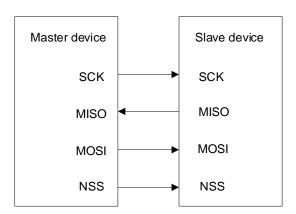

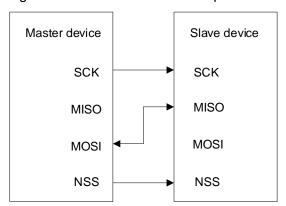

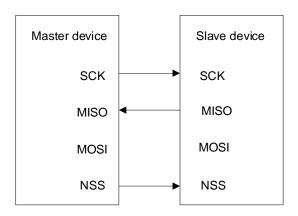

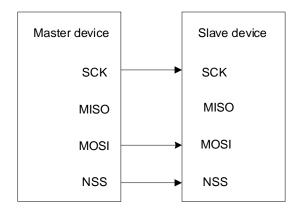

| 22.5 | SPI Functional Description                                    | 310  |

| 22.6 | I2S Functional Description                                    | 321  |

| 22.7 | Register Address Mapping                                      | 331  |

| 22.8 | Register Functional Description                               | 331  |

| 23   | HDMI-CEC Controller (HDMI-CEC) ·······                        | 339  |

| 23.1 | Introduction                                                  | 339  |

| 23.2 | Main Characteristics                                          | 339  |

| 23.3 | Structure Block Diagram                                       | 339  |

| 23.4 | Main Functions                                                | 339  |

| 23.5 | Register Address Mapping                        | 342 |

|------|-------------------------------------------------|-----|

| 23.6 | Register Functional Description                 | 342 |

| 24   | Analog-to-digital Converter (ADC)               | 348 |

| 24.1 | Introduction                                    | 348 |

| 24.2 | Main Characteristics                            | 348 |

| 24.3 | Functional Description                          | 349 |

| 24.4 | Register Address Mapping                        | 353 |

| 24.5 | Register Functional Description                 | 354 |

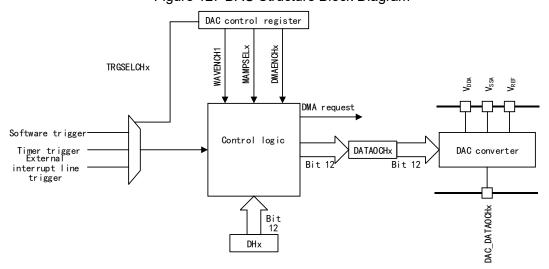

| 25   | Digital-to-analog Converter (DAC) ······        | 360 |

| 25.1 | Introduction                                    | 360 |

| 25.2 | Main Characteristics                            | 360 |

| 25.3 | Structure Block Diagram                         | 360 |

| 25.4 | Functional Overview                             | 361 |

| 25.5 | Register Address Mapping                        | 362 |

| 25.6 | Register Functional Description                 | 363 |

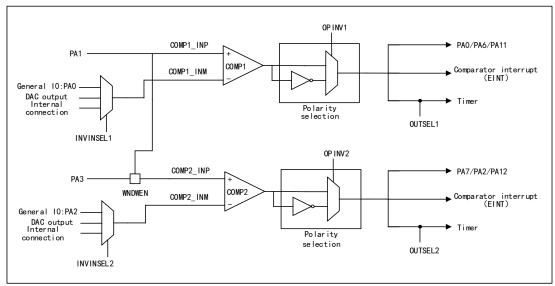

| 26   | Comparator (COMP) ······                        | 366 |

| 26.1 | Full Name and Abbreviation Description of Terms | 366 |

| 26.2 | Introduction                                    | 366 |

| 26.3 | Main Characteristics                            | 366 |

| 26.4 | Structure Block Diagram                         | 366 |

| 26.5 | Functional Description                          | 367 |

| 26.6 | Register Address Mapping                        | 368 |

| 26.7 | Register Functional Description                 |     |

| 27   | Touch Sensing Controller (TSC)                  | 371 |

| 27.1 | Overview                                        | 371 |

| 27.2 | Main Characteristics                            | 371 |

| 27.3 | Structure Block Diagram                         | 372 |

| 27.4 | Functional Description                          | 372 |

| 27.5 | Register Address Mapping                        | 375 |

| 27.6 | Register Functional Description                 | 375 |

| 28   | Cyclic Redundancy Check Computing Unit (CRC)    | 380 |

| 28.1 | Introduction                                    | 380 |

| 28.2 | Functional Description                          | 380 |

| 28.3 | Register Address Mapping                        | 380 |

| 28.4 | Register Functional Description                 | 381 |

| 29   | Chip Electronic Signature                       | 383 |

| 29.1 | Introduction                                    | 383 |

| version instory                 | - 504 |

|---------------------------------|-------|

| Varsion History                 | .384  |

| Register Functional Description | 383   |

| Functional Description          | 383   |

|                                 | ·     |

# 1 Introduction and Document Description Rules

### 1.1 Introduction

This reference manual provides application developers with all the information about how to use MCU (micro-controller) system architecture, memory and peripherals.

For information about Arm® Cortex® -M0+ core, please refer to Arm® Cortex® -M0+ Technical Reference Manual; please refer to the corresponding datasheet for detailed data such as model information, dimension and electrical characteristics of the device; for all MCU series models, please refer to the corresponding data manual for memory mapping, peripheral existence and their number.

It is hereby declared that Geehy Semiconductor Co., Ltd., hereinafter refer to as "Geehy".

### 1.2 Document Description Rules

### 1.2.1 "Register Functional Description" Rules

- (1) Control (CTRL) registers are all "set to 1 and cleared by software", unless otherwise specified.

- (2) The control registers are usually followed by verb abbreviations to make a distinction. The verbs can be: EN-Enable, CFG-Configure, D-Disable, SET-Setup and SEL-Select

- (3) The state register abbreviation is usually followed by FLG to make a difference.

- (4) The value and data registers usually include V, VALUE, D and DATA, which are not followed by verbs, such as: xxPSC and CNT.

### 1.2.2 Full Name and Abbreviation Description of Terms

Table 1 R/W Abbreviation and Description

| R/W                     | Description                                                                                                         | Abbreviation |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|--------------|

| read/write              | Software can read and write this bit.                                                                               | R/W          |

| read-only               | Software can only read this bit.                                                                                    | R            |

| write-only              | Software can only write this bit, and after reading this bit, the reset value will be returned.                     | W            |

| read/clear              | The software can read this bit and clear it by writing 1. Writing 0 has no effect on this bit.                      | RC_W1        |

| read/clear              | The software can read this bit and clear it by writing 0. Writing 1 has no effect on this bit.                      | RC_W0        |

| read/clear by read      | The software can read this bit, reading this bit will automatically clear it to 0, and writing this bit is invalid. | RC_R         |

| read/set                | The software can read and set this bit, and writing 0 has no effect on this bit.                                    | R/S          |

| read-only write trigger | The software can read this bit and writing 0 or 1 can trigger an event but has no effect on the value of            | RT_W         |

| R/W    | Description                                                                               | Abbreviation |

|--------|-------------------------------------------------------------------------------------------|--------------|

|        | this bit.                                                                                 |              |

| toggle | The software can flip this bit only by writing 1 and writing 0 has no effect on this bit. | Т            |

Table 2 Functional Description and Full Name and Abbreviation of Terms of Commonly Used Registers

| Used Registers  Full name in English English abbreviation |  |  |  |

|-----------------------------------------------------------|--|--|--|

| English abbreviation                                      |  |  |  |

| EN                                                        |  |  |  |

| D                                                         |  |  |  |

| CLR                                                       |  |  |  |

| SEL                                                       |  |  |  |

| CFG                                                       |  |  |  |

| CTRL                                                      |  |  |  |

| С                                                         |  |  |  |

| RST                                                       |  |  |  |

| STOP                                                      |  |  |  |

| SET                                                       |  |  |  |

| LD                                                        |  |  |  |

| CAL                                                       |  |  |  |

| INIT                                                      |  |  |  |

| ERR                                                       |  |  |  |

| STS                                                       |  |  |  |

| RDY                                                       |  |  |  |

| SW                                                        |  |  |  |

| HW                                                        |  |  |  |

| SRC                                                       |  |  |  |

| SYS                                                       |  |  |  |

| PER                                                       |  |  |  |

| ADDR                                                      |  |  |  |

| DIR                                                       |  |  |  |

| CLK                                                       |  |  |  |

|                                                           |  |  |  |

| 1                                                         |  |  |  |

| 0                                                         |  |  |  |

|                                                           |  |  |  |

| Full name in English | English abbreviation |

|----------------------|----------------------|

| Data                 | DATA                 |

| Size                 | SIZE                 |

| Divider              | DIV                  |

| Prescaler            | PSC                  |

| Multiplier           | MUL                  |

| Period               | PRD                  |

Table 3 Full Name and Abbreviation of Modules

| Full name in English                                    | English abbreviation |

|---------------------------------------------------------|----------------------|

| Reset and Clock Management                              | RCM                  |

| Power Management Unit                                   | PMU                  |

| Nested Vector Interrupt Controller                      | NVIC                 |

| External Interrupt /Event Controller                    | EINT                 |

| Direct Memory Access                                    | DMA                  |

| Debug MCU                                               | DBG MCU              |

| General-Purpose Input Output Pin                        | GPIO                 |

| Alternate Function Input Output Pin                     | AFIO                 |

| Timer                                                   | TMR                  |

| Watchdog Timer                                          | WDT                  |

| Independent Watchdog Timer                              | IWDT                 |

| Windows Watchdog Timer                                  | WWDT                 |

| Real-Time Clock                                         | RTC                  |

| Universal Synchronous Asynchronous Receiver Transmitter | USART                |

| Inter-integrated Circuit Interface                      | I2C                  |

| Serial Peripheral Interface                             | SPI                  |

| Inter-IC Sound Interface                                | 128                  |

| HDMI-CEC Controller                                     | HDMI-CEC             |

| Analog-to-Digital Converter                             | ADC                  |

| Digital-to-Analog Converter                             | DAC                  |

| Touch Sensing Controller                                | TSC                  |

| Comparator                                              | COMP                 |

| Cyclic Redundancy Check Calculation Unit                | CRC                  |

# 2 System Architecture

# 2.1 Full Name and Abbreviation Description of Terms

Table 4 Full Name and Abbreviation Description of Terms

| Full name in English          | English abbreviation |  |

|-------------------------------|----------------------|--|

| Advanced High-Performance Bus | АНВ                  |  |

| Advanced Peripheral Bus       | APB                  |  |

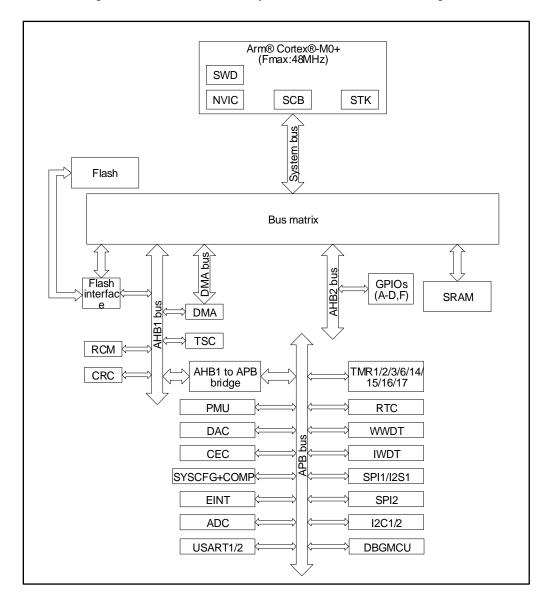

# 2.2 System Architecture Block Diagram

The main system mainly consists of two master modules and four slave modules. The main modules are Arm® Cortex®-M0+ core and general-purpose DMA (five channels). The slave modules are internal SRAM, internal flash memory Flash, AHB2 bus connecting all GPIO ports, and AHB1/APB bridge on AHB1 bus, among which, AHB1/APB bridge connects all peripherals.

These are connected through a multi-level AHB bus architecture, as shown in the figure below:

Figure 1 APM32F051x6x8 System Architecture Block Diagram

Table 5 Bus Name

| Name              | Instruction                                                                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System bus        | Connect the system bus (peripheral bus) of $\mathrm{Arm}^{\$}$ Cortex $^{\$}$ -M0+ core and the bus matrix.                                                                                                                      |

| DMA bus           | Connect AHB master control interface of DMA and the bus matrix.                                                                                                                                                                  |

| Bus matrix        | Coordinate the access of the core and DMA; consist of CPU AHB, system bus, DMA bus and FMC, SRAM, AHB2 and AHB1/APB bridge. AHB peripheral is connected with the system bus through the bus matrix and is allowed to access DMA. |

| AHB/APB<br>bridge | The bridge provides synchronous connection between AHB and APB buses.  The non-32-bit access to APB register will be converted into 32 bits automatically.                                                                       |

# 2.3 Memory Mapping

The memory mapping address is totally 4GB address. The assigned addresses include the core (including core peripherals), on-chip Flash (including main

memory area, system memory area and option bytes), on-chip SRAM, and bus peripherals (including AHB and APB peripherals). Please refer to the data manual of the corresponding model for specific information of various addresses.

#### 2.3.1 Embedded SRAM

Built-in static SRAM. It can access by byte, half word (16 bits) or full word (32 bits). The start address of SRAM is 0x2000 0000.

# 2.4 Startup Configuration

APM32F MCU series realizes a special mechanism. By configuring the BOOT pin parameter and the nBOOT1 bit in FMC\_OBCS, there are three different startup modes, namely, the system can not only start from Flash memory or system memory, but also start from the built-in SRAM. The memory selected as the start zone is determined by the selected startup mode.

Table 6 Startup Mode Configuration and Access Mode

|               | up mode<br>guration Startup mode |                              | Access mode                                                                                                                                                                              |  |

|---------------|----------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nBOOT1<br>bit | BOOT0<br>Pin                     | Startup mode                 | Access mode                                                                                                                                                                              |  |

| Х             | 0                                | Main flash memory<br>(Flash) | The main flash memory is mapped to the boot space, but it can still be accessed at its original address, that is, the contents of the flash memory can be accessed in two address areas. |  |

| 1             | 1                                | System memory                | The system memory is mapped to the boot space (0x0000 0000), but it can still be accessed at its original address.                                                                       |  |

| 0             | 1                                | Built-in SRAM                | SRAM can be accessed only at the starting address.                                                                                                                                       |  |

### Note:

- (1) The boot space address is 0x0000 0000

- (2) The original address of Flash is 0x0800 0000

- (3) The original address of the system memory is 0x1FFF EC00

- (4) The starting address of SRAM is 0x2000 0000

- (5) The user can select the startup mode after reset by setting the states of nBOOT1 bit and BOOT0 pin.

- (6) BOOT pin should keep the user's required startup configuration in standby mode. When exiting from the standby mode, the value of boot pin will be latched.

- (7) If you choose to start from built-in SRAM, you must use NVIC's exception table and offset register to remap the vector table to SRAM when writing the application code.

### Physical remapping

After nBOOT1 bit and BOOT0 pin are selected, MMSEL bit of SYSCFG\_CFG1

register can be modified through software program, and the accessed memory can be modified. See SYSCFG register for specific configuration.

### **Embedded startup program**

The embedded startup program is written on the production line by Geehy and stored in the system memory area.

# 3 FLASH Memory

This chapter mainly introduces the storage structure, read, erase, write, read/write protection, unlock/lock characteristics of Flash, and the involved register functional description.

# 3.1 Full Name and Abbreviation Description of Terms

Table 7 Full Name and Abbreviation Description of Terms

| Full name in English    | English abbreviation |

|-------------------------|----------------------|

| Flash Memory Controller | FMC                  |

### 3.2 Main Characteristics

- (1) Flash memory structure

- Contain main memory area and information block

- The capacity of main memory area is up to 64KB

- The information block is divided into system memory area and option byte

- BootLoader program, 96-bit unique UID and capacity information of main storage area are stored in system memory area, with a capacity of 3KB

- The capacity of the option byte area is 16Bytes

- (2) Functional Description

- Read Flash

- Page/Card erase Flash

- Write Flash

- Read/White protection Flash

- Configure option bytes

# 3.3 Flash Memory Structure

Table 8 Flash Memory Structure of APM32F051x6x8 Series Products

| Block            | Name    | Address area            | Size (byte) | Sector   |

|------------------|---------|-------------------------|-------------|----------|

| Main memory area | Page 0  | 0x0800 0000–0x0800 03FF | 1K          |          |

| Main memory area | Page 1  | 0x0800 0400-0x0800 07FF | 1K          | Sector 0 |

| Main memory area | Page 2  | 0x0800 0800-0x0800 0BFF | 1K          | Sector 0 |

| Main memory area | Page 3  | 0x0800 0C00-0x0800 0FFF | 1K          |          |

| Main memory area | •••     |                         |             |          |

| Main memory area | Page 28 | 0x0800 7000–0x0800 73FF | 1K          |          |

| Main memory area | Page 29 | 0x0800 7400–0x0800 77FF | 1K          | Sector 7 |

| Main memory area | Page 30 | 0x0800 7800-0x0800 7BFF | 1K          | Sector 7 |

| Main memory area | Page 31 | 0x0800 7C00-0x0800 7FFF | 1K          |          |

| Main memory area | •••     |                         |             |          |

| Block             | Name Address area  |                         | Size (byte) | Sector |

|-------------------|--------------------|-------------------------|-------------|--------|

| Main memory area  | Page 60            | 0x0800 F000-0x0800 F3FF | 1K          |        |

| Main memory area  | Page 61            | 0x0800 F400-0x0800 F7FF | 1K          | Sector |

| Main memory area  | Page 62            | 0x0800 F800-0x0800 FBFF | 1K          | 15     |

| Main memory area  | Page 63            | 0x0800 FC00-0x0800 FFFF | 1K          |        |

| Information block | System memory area | 0x1FFF EC00-0x1FFF F7FF | 3K          | -      |

| Information block | Option byte        | 0x1FFF F800–0x1FFF F80F | 16          | -      |

Note: The number of pages in the main memory block of APM32F051x6x8 series products is related to the Flash capacity of specific product.

### 3.4 Functional Description

Describe the operation of main memory and information block (including system memory area and option byte), including read, write, erase and read/write protection.

Reading Flash includes main memory block and information block, while the erase, write, read/write are introduced separately; the system memory area has been written before the product leaves the factory and cannot be modified by the user. The erase, write, and read/write protection of the module will not be introduced.

### 3.4.1 Read Flash

Flash memory can be directly addressed, and reading Flash is affected by the following configuration:

### Wait cycle

Different waiting periods should be configured for different system clocks:

• 0 wait cycle: 0<system clock≤24MHz

• 1 wait cycle: 24MHz<system clock≤48MHz

#### Prefetch buffer

It can improve the reading speed and every time it is reset, the prefetch buffer will be automatically opened; the read interface with prefetch buffer. It can be configured only when the system clock is consistent with AHB clock and is less than 24MHz, and can be used only when the system clock is consistent with AHB clock

### Half-cycle access

When the power consumption needs to be optimized, half-cycle access can be used; at this time, the system clock and AHB clock are consistent, and the system clock is 8MHz or less than 8MHz, then half-cycle access to Flash can be used, otherwise, it must be turned on.

### 3.4.2 Main Memory Block

#### 3.4.2.1 Erase main memory block

FMC supports page erase and mass erase (full erase) to initialize the contents of the main memory area to high level (the data is represented as 0xFFFF). Before

writing to Flash, users are advised to erase the write address page. If the data of write address is not 0xFFFF, a programming error will be triggered.

### Main memory page erase

Page erase is an independent erase according to the main memory area page selected by the program, which will not have any impact on the page not selected for erasure.

After the correct page erase (or flash write operation) is completed, OCF bit in FMC\_STS register will be set. If OCIE interrupt is enabled, an operation completion interrupt will be triggered. Users need to note that the page to be erased must be a valid page (the valid address of the main memory area and the address without write protection).

### Main memory mass erase

The mass erase operation will erase all the contents in the main storage area of Flash, and the mass erase operation will erase all the data in the main memory area, so the users need to pay special attention when using it to avoid the loss of important data caused by misoperation.

### 3.4.2.2 Write main memory block

FMC supports the writing of 16-bit (half word) data in the main memory area. You can select Debug, BootLoader, program running in SRAM, and directly reading the erased page to judge whether the erasing is successful.

In order to ensure correct writing, it is necessary to check whether the destination address has been erased before writing; if it is not erased, the written data will be invalid and PEF bit of FMC\_STS register will be set to "1". If the destination address has write protection, the written data is invalid and a write protection error will be triggered (WPEF bit of FMC\_STS is set to "1").

### 3.4.2.3 Main memory block of read/write protection

Read/Write protection of the flash is used to prevent illegal reading/modification of the main memory area code or data, and it is controlled by the read/write protection configuration byte of option byte. For APM32F051x6x8 series products, the basic unit of write protection is 4 pages (i.e. 4KB).

#### **Read protection**

The read protection has three levels, namely, Level 0, Level 1 and Level 2, which are specifically described as follows:

Table 9 Difference among Read Protection Levels

| Category | READPROT                                | Description                                                                                                                                                                                                                                                                                                                  |

|----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level 0  | 0xAA                                    | The main memory area and option byte are erasable, writable and readable.                                                                                                                                                                                                                                                    |

| Level 1  | Other values<br>except 0xAA and<br>0xCC | User mode: Allowed to erase, write and read the main memory area and option byte.  Debug, SRAM running, system memory area running: Access to the main memory area is disabled; the option byte is erasable, writable and readable, but when the level is modified to 0, the main memory area erase will be performed first. |

| Level 2  | 0xCC                                    | Debug is not allowed, the main memory area and option byte cannot be erased, written and read, and the level cannot be modified.                                                                                                                                                                                             |

### Write protection

Write protection control can be conducted for the corresponding page of the

main memory block by configuring the value of write protection option byte WRP0/1. After the write protection is turned on, the content on the corresponding page of the main memory area cannot be modified in any way.

### 3.4.2.4 Main memory block of unlock/lock

FMC\_CTRL1 of the reset FMC will be locked by hardware, and then FMC\_CTRL1 can't be directly written, and the corresponding value must be written to FMC\_KEY according to the correct sequence to unlock FMC. The KEY value is as follows:

- KEY1=0x45670123

- KEY2=0xCDEF89AB

The wrong writing sequence or wrong value will cause the program to enter the hardware wrongly. At this time, FMC will be locked, and all FMC operations will be invalid until it is reset next time. The users can also lock FMC through software by writing "1" to LOCK bit of the control register 2 (FMC CTRL2).

In each Flash programming operation, the users must follow the steps of "Flash unlock - program by user - Flash lock", so as to avoid the risk that user code/data is accidentally modified due to the Flash unlocking after the Flash programming operation.

### 3.4.3 Option Byte

### 3.4.3.1 Erase option byte

Support erase function. After the correct option byte erase (or option byte write operation) is completed, OCF of FMC\_STS register will be set. If OCIE interrupt is enabled, an operation completion interrupt will be triggered.

### 3.4.3.2 Write option byte

Eight configurable bytes of option bytes all support writing function.

### 3.4.3.3 Option byte of write protection

By default, the option byte is always readable and write protected. To perform write operation (program/erase) for the option byte block, first write the correct key sequence (the same as that of locking) in FMC\_OBKEY, and then allow the write operation of option byte block; the OBWEN bit of FLASH\_CTRL2 register indicates write enabled; clear this bit and write operation will be disabled.

### 3.4.3.4 Unlock/Lock option byte

After the system reset, the option byte is locked by default. Only when the option byte is unlocked correctly, can it be modified. The difference between option byte unlocking and flash unlocking is that FMC\_OBKEY register rather than FMC\_KEY register writes the KEY value. The option byte does not support "software lock". The user should pay special attention to that every time after the value of the option byte is modified, the system must be reset to make it effective.

### 3.4.4 Function Description of Option Byte

The option byte provides some optional functions for users, and it mainly consists of 8 configurable bytes and corresponding complementary codes. Every time the system is reset, the option byte area will be reloaded to the FMC\_OBCS and FMC\_WRTPROT register (the option byte will only take effect each time they are reloaded to FMC). In the process of reloading, if a certain configurable byte does not match its reverse code, an option byte error (OBE bit of FMC\_register is set to "1") will be triggered, and this byte will be set to "0xFF".

# The information of 16 bytes in the option byte area is shown in the table below.

Table 10 Option Bytes

| Address     | Option byte | Table 10 Initial value | R/W | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1FFF F800 | READPROT    | 0xAA                   | R/W | Read protection configuration Bit [7:0]: READPROT 0xAA: Level 0 0xCC: Level 2 Others: Level 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x1FFF F801 | nREADPROT   | 0x55                   | R   | READPROT complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x1FFF F802 | UOB         | 0xFF                   | R/W | User option byte Bit 0: WDTSEL  0: Hardware watchdog 1: Software watchdog Bit 1: RSTSTOP  0: Reset occurs when entering the Stop mode 1: Reset does not occur when entering the Stop mode Bit 2: RSTSTDB  0: Reset occurs when entering the Standby mode 1: Reset does not occur when entering the Standby mode Bit 3: Reserved Bit 3: Reserved Bit 4: nBOOT1 Select BOOT mode Bit 5: VDDAMONI  0: VDDA power supply detector is disabled 1: VDDA power supply detector is enabled Bit 6: SRAMPARITY  0: RAM parity check is disabled 1: RAM parity check is enabled Bit 7: Reserved |

| 0x1FFF F803 | nUOB        | 0x00                   | R   | UOB complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x1FFF F804 | Data0       | 0xFF                   | R/W | User data byte 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1FFF F805 | nData0      | 0x00                   | R   | Data0 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x1FFF F806 | Data1       | 0xFF                   | R/W | User data byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1FFF F807 | nData1      | 0x00                   | R   | Data complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x1FFF F808 | WRP0        | 0xFF                   | R/W | Write protection configuration 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1FFF F809 | nWRP0       | 0x00                   | R   | WRP0 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x1FFF F80A | WRP1        | 0xFF                   | R/W | Write protection configuration 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1FFF F80B | nWRP1       | 0x00                   | R   | WRP1 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x1FFF F80C | WRP2        | 0xFF                   | R/W | Write protection configuration 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1FFF F80D | nWRP2       | 0x00                   | R   | WRP2 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x1FFF F80E | WRP3        | 0xFF                   | R/W | Write protection configuration 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x1FFF F80F | nWRP3       | 0x00                   | R   | WRP3 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Note: When the configurable byte and its reverse code value are "0xFF", the match will not be verified in the reloading process

Table 11 Write Protection WRPx Function Description of Main Memory Area

| Product capacity            | Functional description                                                                                                                                                                                 |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APM32F051x6 series products | Each bit in WRPx controls the write protection of 4KB (4 pages) address of the main memory area 0: Write protection is turned on 1: Write protection is not turned on WRP0: Page 0-31                  |

| APM32F051x8 series products | Each bit in WRPx controls the write protection of 4KB (4 pages) address of the main memory area 0: Write protection is turned on 1: Write protection is not turned on WRP0: Page 0-31 WRP1: Page 32-63 |

Note: Flash read/write protection configuration is independent of each other. Removing the write protection will not force the loss of the contents of the main memory area, but keep them as they are.

# 3.5 Register Address Mapping

Base address: 0x40022000

Table 12 FMC Register Address Mapping

| Register name | Description                        | Offset address |

|---------------|------------------------------------|----------------|

| FMC_CTRL1     | Control register 1                 | 0x00           |

| FMC_KEY       | Key register                       | 0x04           |

| FMC_OBKEY     | Option byte key register           | 0x08           |

| FMC_STS       | State register                     | 0x0C           |

| FMC_CTRL2     | Control register 2                 | 0x10           |

| FMC_ADDR      | Address register                   | 0x14           |

| FMC_OBCS      | Option byte control/state register | 0x1C           |

| FMC_WRTPROT   | Write protection register          | 0x20           |

# 3.6 Register Functional Description

# 3.6.1 Control register 1 (FMC\_CTRL1)

Offset address: 0x00

Reset value: 0x0000 0000

| Field | Name                                                                                                                                                                                                                                                                                                       | R/W      | Description                                                                                                             |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------|--|

| 2:0   | WS R/W Wait State Configure 000: 0 wait cycle, 0 <system 001:="" 1="" 24mhz<system="" clock≤24mhz="" clock≤48m="" cycle:="" others:="" reserved<="" td="" wait=""><td>000: 0 wait cycle, 0<system clock≤24mhz<br="">001: 1 wait cycle: 24MHz<system clock≤48mhz<="" td=""></system></system></td></system> |          | 000: 0 wait cycle, 0 <system clock≤24mhz<br="">001: 1 wait cycle: 24MHz<system clock≤48mhz<="" td=""></system></system> |  |

| 3     |                                                                                                                                                                                                                                                                                                            | Reserved |                                                                                                                         |  |

| 4     | PBEN                                                                                                                                                                                                                                                                                                       | R/W      | Prefetch Buffer Enable 0: Disable 1: Enable                                                                             |  |

| 5     | PBSF                                                                                                                                                                                                                                                                                                       | R        | Prefetch Buffer Status Flag 0: In disabled state 1: In enabled state                                                    |  |

| Field | Name | R/W | Description |

|-------|------|-----|-------------|

| 31:6  |      |     | Reserved    |

# 3.6.2 Key register (FMC\_KEY)

Offset address: 0x04

Reset value: xxxx xxxx

| Field | Name | R/W | Description                                                                                                                                                         |

|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0  | KEY  | W   | FMC Key Writing the keys represented by these bits can unlock FMC. These bits can only perform write operation, and 0 is returned when read operation is performed. |

# 3.6.3 Option byte key register (FMC\_OBKEY)

Offset address: 0x08 Reset value: xxxx xxxx

| Field | Name  | R/W | Description                                                                                                                                                                                            |

|-------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0  | OBKEY | W   | Option Byte Key Writing the keys represented by these bits can unlock the option byte write operation. These bits can only perform write operation and 0 is returned when read operation is performed. |

### 3.6.4 State register (FMC\_STS)

Offset address: 0x0C

Reset value: 0x0000 0000

| Field | Name     | R/W      | Description                                                                                                                                                          |  |  |  |

|-------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | BUSYF    | R        | Busy Flag This bit indicates that a flash operation is in progress. State bits can only perform write operation, and 0 is returned when read operation is performed. |  |  |  |

| 1     |          |          | Reserved                                                                                                                                                             |  |  |  |

| 2     | PEF      | R/W      | Programming Error Flag This bit will be set by software when the value before the address is edited is not "0xFFFF".                                                 |  |  |  |

| 3     |          | Reserved |                                                                                                                                                                      |  |  |  |

| 4     | WPEF     | R/W      | Write Protection Error Flag This bit will be set by hardware when programming the write protection address in FLASH.                                                 |  |  |  |

| 5     | OCF      | R/W      | Operation Complete Flag This bit will be set by hardware when read/write operation in FLASH is completed.                                                            |  |  |  |

| 31:6  | Reserved |          |                                                                                                                                                                      |  |  |  |

# 3.6.5 Control register 2 (FMC\_CTRL2)

Offset address: 0x10 Reset value: 0x0000 0080

| Field | Name    | R/W | Description                                    |

|-------|---------|-----|------------------------------------------------|

| 0     | PG      | R/W | Program Set this bit to 1 to program Flash     |

| 1     | PAGEERA | R/W | Page Erase Set this bit to 1 to erase the page |

| Field | Name     | R/W                                                                                                                           | Description                                                                                                                                                                           |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2     | MASSERA  | R/W                                                                                                                           | Mass Erase Set this bit to 1 to erase the mass.                                                                                                                                       |

| 3     |          |                                                                                                                               | Reserved                                                                                                                                                                              |

| 4     | OBP      | R/W                                                                                                                           | Option Byte Program Set this bit to 1 to program the option byte.                                                                                                                     |

| 5     | OBE      | R/W                                                                                                                           | Option Byte Erase Set this bit to 1 to erase the option byte.                                                                                                                         |

| 6     | STA      | R/W                                                                                                                           | Start Erase This bit can be only set to 1 by software, and can be reset by clearing STS_BUSYF bit.                                                                                    |

| 7     | LOCK     | R/W                                                                                                                           | Lock This bit can be written to 1 only, and when this bit is set to 1, it means that FMC and CTRL2 registers are locked.                                                              |

| 8     | Reserved |                                                                                                                               |                                                                                                                                                                                       |

| 9     | OBWEN    | R/W                                                                                                                           | Option Byte Write Enable When this bit is set to 1, the option byte can be programmed.                                                                                                |

| 10    | ERRIE    | R/W                                                                                                                           | Error Interrupt Enable  0: Interrupt is disabled  1: Interrupt is enabled  When STS_PEF=1 or STS_WPEF=1, set this bit to generate an interrupt.                                       |

| 11    |          |                                                                                                                               | Reserved                                                                                                                                                                              |

| 12    | OCIE     | R/W                                                                                                                           | Operation Complete Interrupt Enable 0: Operation completion interrupt is disabled 1: Operation completion interrupt is enabled When STS_OCF=1, set this bit to generate an interrupt. |

| 13    | OBLOAD   | Force Option Byte Load When this bit is set to 1, force to reload the option byte to generate reset. 0: Idle 1: Force to load |                                                                                                                                                                                       |

| 31:14 | Reserved |                                                                                                                               |                                                                                                                                                                                       |

### 3.6.6 Address register (FMC\_ADDR)

Offset address: 0x14 Reset value: 0x0000 0000

The register is changed to currently/finally used address by hardware; in page erasing, the register needs to be configured by software.

| Fie | eld | Name | R/W | Description                                                                                                                                                |

|-----|-----|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | 1:0 | ADDR | W   | Flash Address In programming operation, the bit is written to the address to be programmed; in page erasing, this bit is written to the page to be erased. |

### 3.6.7 Option bye control/state register (FMC\_OBCS)

Offset address: 0x1C Reset value: 0xXXXX XX0X

The reset value of the register is related to the value in the written option byte; the reset value of OBE bit is related to the result whether the value of the loaded option byte is consistent with its reverse code.

| Field | Name       | R/W                                             | Description                                                                                                                                                          |  |  |

|-------|------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0     | OBE        | R                                               | Option Byte Error  1: The loaded option byte does not match its complementary code. The option byte and its complementary code are forced to write to 0xFF           |  |  |

| 2:1   | READPROT   | R                                               | Read Protect Enable read protection of different levels. If bit1 is set to 1, it is level 1. If bit2 is set to 1, it is level 2. 00: Level 0 01: Level 1 1X: Level 2 |  |  |

| 7:3   |            |                                                 | Reserved                                                                                                                                                             |  |  |

| 8     | WDTSEL     | R                                               | Watchdog Select 0: Hardware watchdog 1: Software watchdog                                                                                                            |  |  |

| 9     | RSTSTOP    | nReset in STOP Mode 0: Generate 1: Not generate |                                                                                                                                                                      |  |  |

| 10    | RSTSTDB    | R                                               | nReset in STANDBY Mode 0: Generate 1: Not generate                                                                                                                   |  |  |

| 11    |            |                                                 | Reserved                                                                                                                                                             |  |  |

| 12    | nBOOT1     | R                                               | nBoot1 Mode Configure                                                                                                                                                |  |  |

| 13    | VDDAMONI   | R                                               | V <sub>DDA</sub> Monitor                                                                                                                                             |  |  |

| 14    | SRAMPARITY | R                                               | SRAM Parity Check                                                                                                                                                    |  |  |

| 15    | Reserved   |                                                 |                                                                                                                                                                      |  |  |

| 23:16 | DATA0      | R                                               | Data0                                                                                                                                                                |  |  |

| 31:24 | DATA1      | R                                               | Data1                                                                                                                                                                |  |  |

# 3.6.8 Write protection register (FMC\_WRTPROT)

Offset address: 0x20

Reset value: 0xXXXX XXXX (the reset value depends on the programming value

in option bye)

| Field | Name    | R/W | Description                       |

|-------|---------|-----|-----------------------------------|

| 31:0  | WRTPROT | R   | Write Protect 0: Valid 1: Invalid |

# 4 System Configuration Controller (SYSCFG)

### 4.1 Full Name and Abbreviation Description of Terms

Table 13 Full Name and Abbreviation Description of Terms

| Full name in English            | English abbreviation |

|---------------------------------|----------------------|

| Fast Mode Plus                  | FM+                  |

| System Configuration Controller | SYSCFG               |

SYSCFG is mainly used to manage address mapping and control interrupts, specifically: controlling the fast mode plus of I2C on some IO ports; configuring DMA trigger source remapping; remapping from memory to code start area; and managing the external interrupts connected to GPIO.

For details of related configuration, see SYSCFG register configuration.

# 4.2 Register Address Mapping

Table 14 SYSCFG Register Address Mapping

| Register name   | Description                   | Offset address |

|-----------------|-------------------------------|----------------|

| SYSCFG_CFG1     | Configuration register 1      | 0x00           |

| SYSCFG_EINTCFG1 | External interrupt register 1 | 0x08           |

| SYSCFG_EINTCFG2 | External interrupt register 2 | 0x0C           |

| SYSCFG_EINTCFG3 | External interrupt register 3 | 0x10           |

| SYSCFG_EINTCFG4 | External interrupt register 4 | 0x14           |

| SYSCFG_CFG2     | Configuration register 2      | 0x18           |

# 4.3 Register Functional Description

### 4.3.1 Configuration register 1 (SYSCFG CFG1)

Offset address: 0x00

Reset value: 0x0000 000X (X means memory mode, controlled by BOOT. After reset, these bits select the mode configuration parameters through BOOT pin.) This register is used to configure the memory and DMA requested remapping and control the specific I/O pins.

All of these bits can skip the hardware to have the software to select the physical mapping, and can be controlled and reset by software.

| Field | Name  | R/W | Description                                                                                                                                                                                                                                                                             |

|-------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0   | MMSEL | R/W | Memory Mapping Select Control the memory mapping address 0x0000 0000. After reset, the parameters of these bits are determined by actual BOOT. X0: Main flash mapping address: 0x0000 0000 01: System flash mapping address: 0x0000 0000 11: Embedded SRAM mapping address: 0x0000 0000 |

| Field | Name            | R/W | Description                                                                                                                                                                                                                    |

|-------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2   |                 |     | Reserved                                                                                                                                                                                                                       |

| 8     | B ADCDMARMP R/W |     | ADC DMA Request Remap Control remapping request of ADC DMA. 0: No remapping ADC—DMA_CH1 1: Remapping ADC—DMA_CH2                                                                                                               |

| 9     | USART1TXRMP     | R/W | USART1_TX DMA Request Remap This bit controls remapping request of USART1_TX DMA. 0: No remapping USART1_RX—DMA_CH2 1: Remapping USART1_RX—DMA_CH4                                                                             |

| 10    | USART1RXRMP     | R/W | USART1_RX DMA Request Remap This bit controls remapping request of USART1_RX DMA. 0: No remapping USART1_TX—DMA_CH3 1: Remapping USART1_TX—DMA_CH5                                                                             |

| 11    | TMR16DMARMP     | R/W | TMR16 DMA Request Remap This bit controls remapping request of TMR16 DMA. 0: No remapping TMR16_CH1 and TMR16_UP—DMA_CH3 1: Remapping TMR16_CH1 and TMR16_UP—DMA_CH4                                                           |

| 12    | TMR17DMARMP     | R/W | TMR17 DMA Request Remap This bit control remapping request of TMR17. 0: No remapping TMR17_CH1 and TMR17_UP—DMA_CH1 1: Remapping TMR17_CH1 and TMR17_UP—DMA_CH2                                                                |

| 15:13 | Reserved        |     |                                                                                                                                                                                                                                |

| 16    | I2CPB6FMP       | R/W | Fast Mode Plus Driving Capability Activate for PB6 This bit enables PB6 interface to enable I2C fast mode plus. 0: PB6 pin is set as standard mode. 1: PB6 pin is set as I2C fast mode plus and I2C speed control is bypassed. |

| 17    | I2CPB7FMP       | R/W | Fast Mode Plus Driving Capability Activate for PB7 This bit enables PB7 interface to enable I2C fast mode plus. 0: PB7 pin is set as standard mode. 1: PB7 pin is set as I2C fast mode plus and I2C speed control is bypassed. |

| 18    | I2CPB8FMP       | R/W | Fast Mode Plus Driving Capability Activate for PB8 This bit enables PB8 interface to enable I2C fast mode plus. 0: PB8 pin is set as standard mode. 1: PB8 pin is set as I2C fast mode plus and I2C speed control is bypassed. |

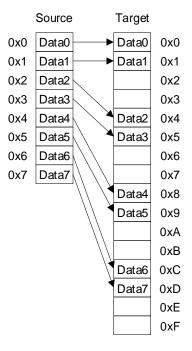

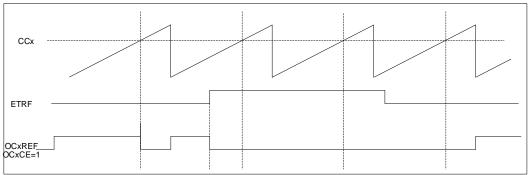

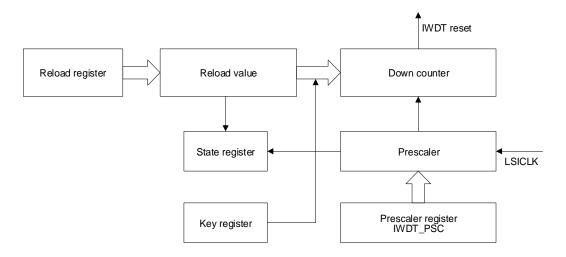

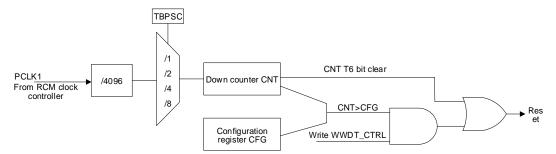

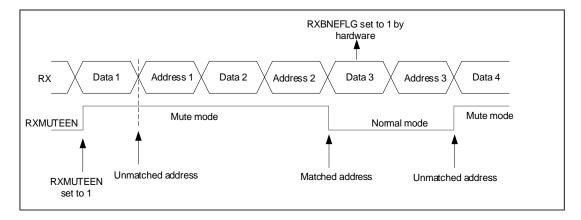

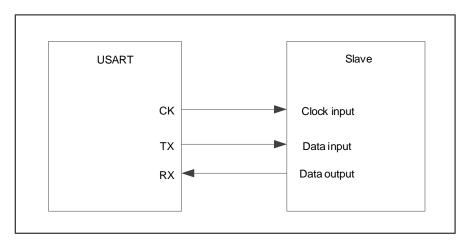

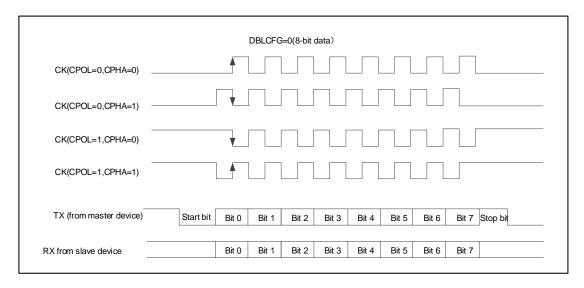

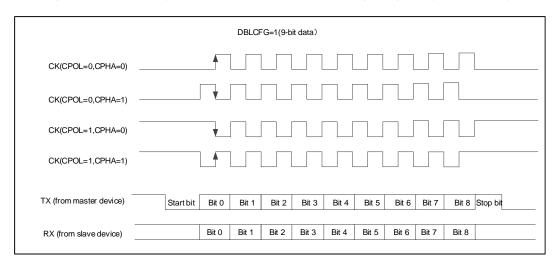

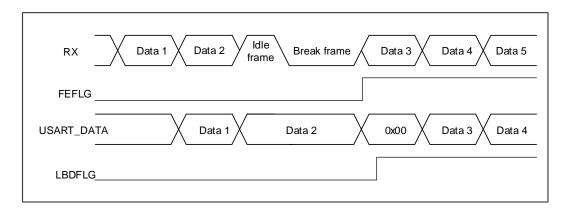

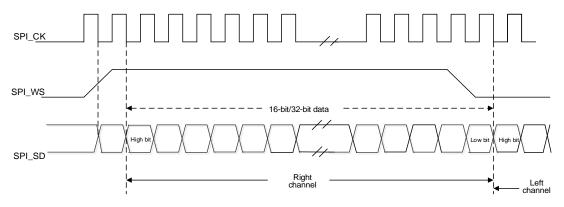

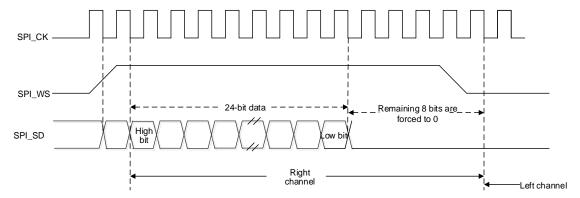

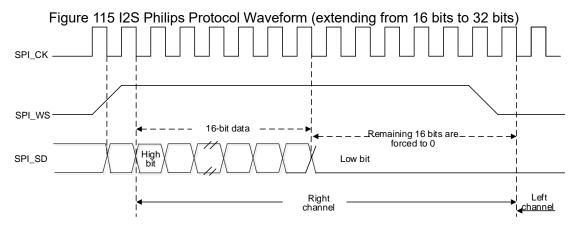

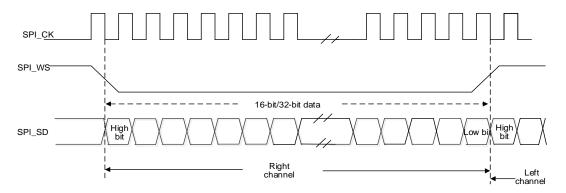

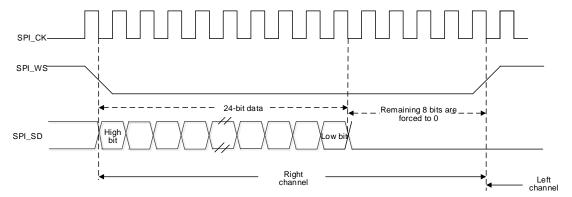

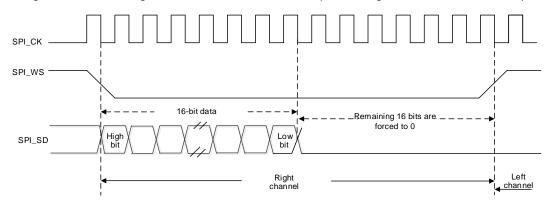

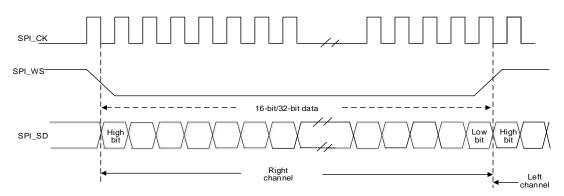

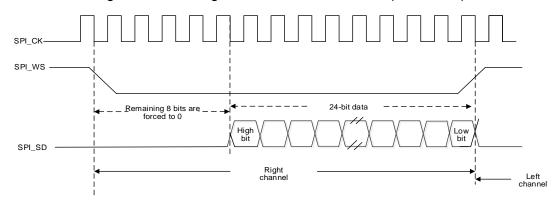

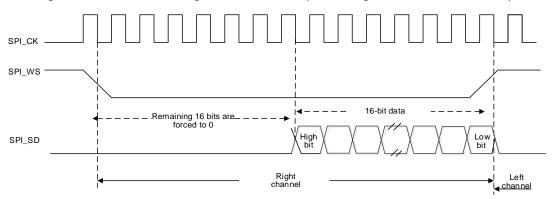

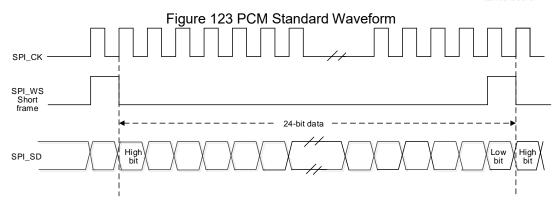

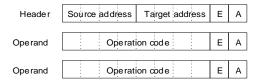

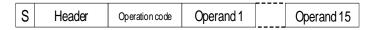

| 19    | I2CPB9FMP       | R/W | Fast Mode Plus Driving Capability Activate for PB9 This bit enables PB9 interface to enable I2C fast mode plus. 0: PB9 pin is set as standard mode. 1: PB9 pin is set as I2C fast mode plus and I2C speed control is           |