NOLOGY 24-Bit High Speed 8-Channel ΔΣ ADCs with Selectable Multiple Reference Inputs DESCRIPTION

### FEATURES

- Five Selectable Differential Reference Inputs

- Four Differential/Eight Single-Ended Inputs

4-Way MUX for Multiple Ratiometric

- Measurements Up to 8kHz Output Rate

- Up to 4kHz Multiplexing Rate

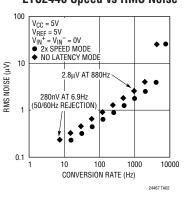

- Selectable Speed/Resolution: 2µV<sub>RMS</sub> Noise at 1.76kHz Output Rate 200nV<sub>RMS</sub> Noise at 13.8Hz Output Rate with Simultaneous 50/60Hz Rejection

- Guaranteed Modulator Stability and Lock-Up Immunity for any Input and Reference Conditions

- 0.0005% INL, No Missing Codes

- Autosleep Enables 20µA Operation at 6.9Hz

- ≤5µV Offset (4.5V < V<sub>CC</sub> < 5.5V, −40°C to 85°C)</p>

- Differential Input and Differential Reference with GND to V<sub>CC</sub> Common Mode Range

- No Latency Mode, Each Conversion is Accurate Even After a New Channel is Selected

- Internal Oscillator—No External Components

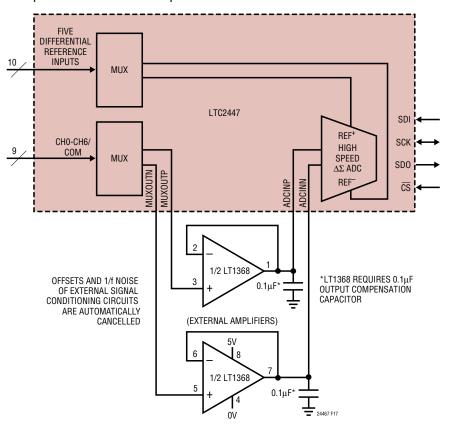

- LTC2447 Includes MUXOUT/ADCIN for External Buffering or Gain

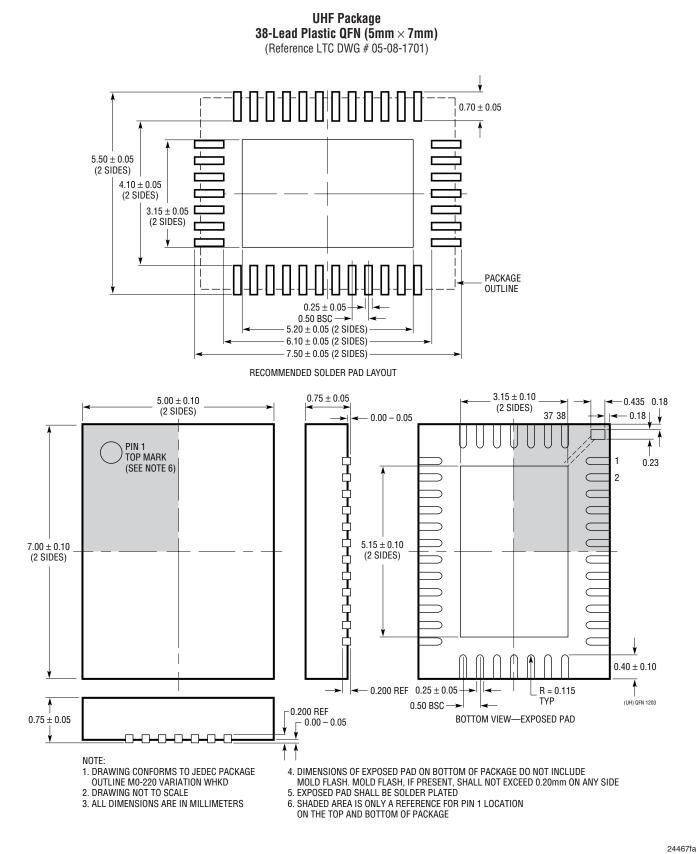

- Tiny QFN 5mm x 7mm Package

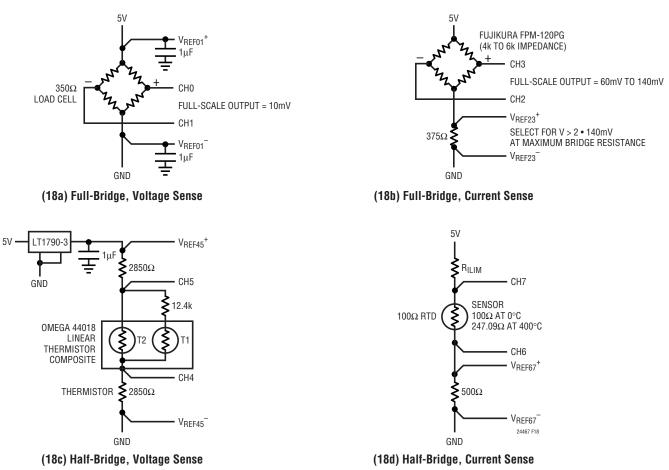

### **APPLICATIONS**

- Flow

- Weight Scales

- Pressure

- Direct Temperature Measurement

- Gas Chromatography

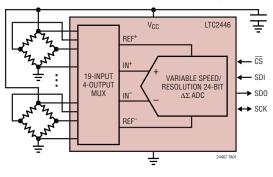

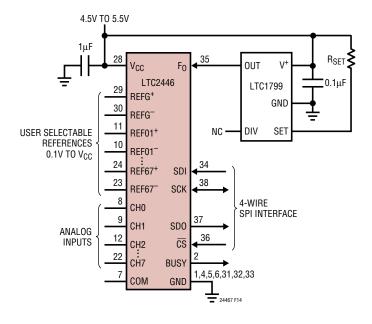

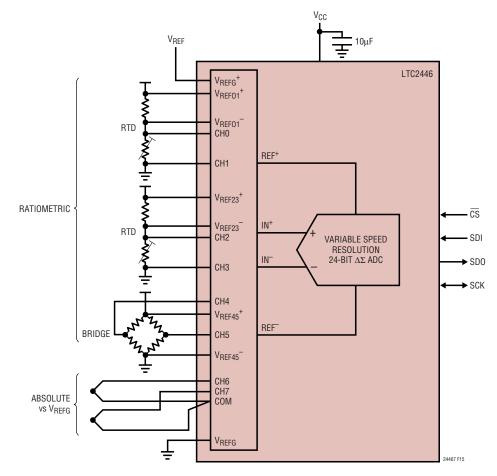

### TYPICAL APPLICATION

Multiple Ratiometric Measurement System

The LTC<sup>®</sup>2446/LTC2447 4-terminal switching enables multiplexed ratiometric measurements. Four sets of selectable differential inputs coupled with four sets of differential reference inputs allow multiple RTDs, bridges and other sensors to be digitized by a single converter. A fifth differential reference input can be selected for any input channel not requiring ratiometric measurements (thermocouples, voltages, current sense, etc.). The flexible input multiplexer allows single-ended or differential inputs coupled with a slaved reference input or a universal reference input.

A proprietary delta-sigma architecture results in absolute accuracy (offset, full-scale, linearity) of 15ppm, noise as low as  $200nV_{RMS}$  and speeds as high as 8kHz. Through a simple 4-wire interface, ten speed/resolution combinations can be selected. The first conversion following a speed, resolution, channel change or reference change is valid since there is no settling time between conversions, enabling scan rates of up to 4kHz. Additionally, a 2x mode can be selected for any speed-enabling output rates up to 8kHz with one cycle of latency.

T, LTC and LT are registered trademarks of Linear Technology Corporation. Protected by U.S. Patents, including 6140950, 6169506, 6208279, 6411242, 6639526

#### LTC2446 Speed vs RMS Noise

### ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| Supply Voltage (V <sub>CC</sub> ) to GND0.3V to 6V               |

|------------------------------------------------------------------|

| Analog Input Pins Voltage                                        |

| to GND $-0.3V$ to (V <sub>CC</sub> + 0.3V)                       |

| Reference Input Pins Voltage                                     |

| to GND0.3V to (V <sub>CC</sub> + 0.3V)                           |

| Digital Input Voltage to GND $-0.3V$ to (V <sub>CC</sub> + 0.3V) |

| Digital Output Voltage to GND0.3 | V to (V <sub>CC</sub> + 0.3V) |

|----------------------------------|-------------------------------|

| Operating Temperature Range      |                               |

| LTC2446C/LTC2447C                | 0°C to 70°C                   |

| LTC2446I/LTC2447I                | –40°C to 85°C                 |

| Storage Temperature Range        | . –65°C to 125°C              |

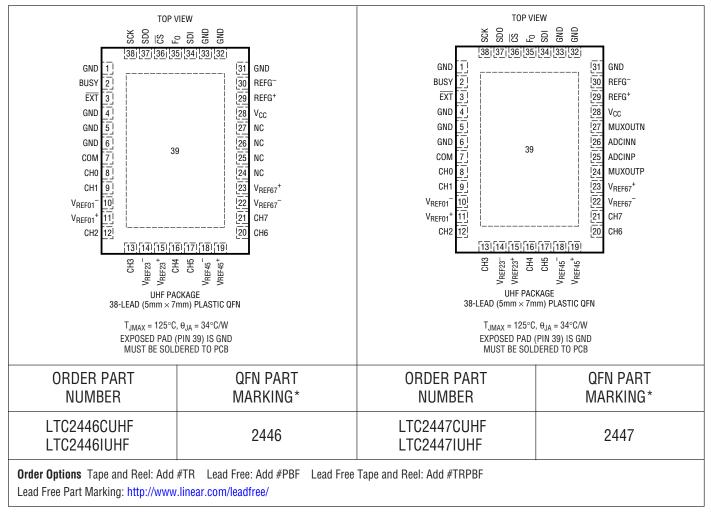

### PACKAGE/ORDER INFORMATION

\*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for parts specified with wider operating temperature ranges.

| PARAMETER                       | CONDITIONS                                                                                                                                                                                                                                                                                                               |   | MIN | ТҮР            | MAX      | UNITS                                                                         |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------------|----------|-------------------------------------------------------------------------------|

| Resolution (No Missing Codes)   | $0.1V \le V_{REF} \le V_{CC}, -0.5 \bullet V_{REF} \le V_{IN} \le 0.5 \bullet V_{REF}, \text{ (Note 5)}$                                                                                                                                                                                                                 |   | 24  |                |          | Bits                                                                          |

| Integral Nonlinearity           | $V_{CC} = 5V, REF^+ = 5V, REF^- = GND, V_{INCM} = 2.5V, (Note 6)$<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, V <sub>INCM</sub> = 1.25V, (Note 6)                                                                                                                                                                | • |     | 5<br>3         | 15       | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub>                            |

| Offset Error                    | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC}, \ REF^- = GND, \\ GND \leq IN^+ = IN^- \leq V_{CC} \ (Note \ 12) \end{array}$                                                                                                                                                                                             | • |     | 2.5            | 5        | μV                                                                            |

| Offset Error Drift              | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC}, \ REF^- = GND, \\ GND \leq IN^+ = IN^- \leq V_{CC} \end{array}$                                                                                                                                                                                                           |   |     | 20             |          | nV/°C                                                                         |

| Positive Full-Scale Error       | REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 3.75V, IN <sup>-</sup> = 1.25V<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 1.875V, IN <sup>-</sup> = 0.625V                                                                                                                   | • |     | 10<br>10       | 50<br>50 | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub>                            |

| Positive Full-Scale Error Drift | $2.5V \le REF^+ \le V_{CC}, REF^- = GND,$<br>IN <sup>+</sup> = 0.75REF <sup>+</sup> , IN <sup>-</sup> = 0.25 • REF <sup>+</sup>                                                                                                                                                                                          |   |     | 0.2            |          | ppm of V <sub>REF</sub> /°C                                                   |

| Negative Full-Scale Error       | REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 1.25V, IN <sup>-</sup> = 3.75V<br>REF <sup>+</sup> = 2.5V, REF <sup>-</sup> = GND, IN <sup>+</sup> = 0.625V, IN <sup>-</sup> = 1.875V                                                                                                                   | • |     | 10<br>10       | 50<br>50 | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub>                            |

| Negative Full-Scale Error Drift | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC},  REF^- = GND, \\ IN^+ = 0.25 \bullet REF^+,  IN^- = 0.75 \bullet REF^+ \end{array}$                                                                                                                                                                                       |   |     | 0.2            |          | ppm of V <sub>REF</sub> /°C                                                   |

| Total Unadjusted Error          | $ \begin{array}{l} 5V \leq V_{CC} \leq 5.5V, \mbox{ REF}^+ = 2.5V, \mbox{ REF}^- = \mbox{ GND},  V_{INCM} = 1.25V \\ 5V \leq V_{CC} \leq 5.5V, \mbox{ REF}^+ = 5V, \mbox{ REF}^- = \mbox{ GND},  V_{INCM} = 2.5V \\ \mbox{ REF}^+ = 2.5V, \mbox{ REF}^- = \mbox{ GND},  V_{INCM} = 1.25V, \mbox{ (Note 6)} \end{array} $ |   |     | 15<br>15<br>15 |          | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub> |

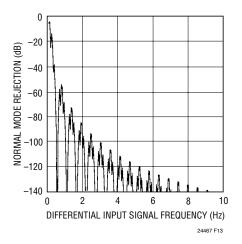

| Input Common Mode Rejection DC  | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC},  REF^- = GND, \\ GND \leq IN^- = IN^+ \leq V_{CC} \end{array}$                                                                                                                                                                                                            |   |     | 120            |          | dB                                                                            |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Notes 3, 4)

# **ANALOG INPUT AND REFERENCE** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL                                        | PARAMETER                                                                      | CONDITIONS                                                                                                |   | MIN                  | ТҮР        | MAX                    | UNITS |

|-----------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---|----------------------|------------|------------------------|-------|

| IN <sup>+</sup>                               | Absolute/Common Mode IN <sup>+</sup> Voltage                                   |                                                                                                           |   | GND – 0.3V           |            | V <sub>CC</sub> + 0.3V | V     |

| IN <sup>-</sup>                               | Absolute/Common Mode IN <sup>-</sup> Voltage                                   |                                                                                                           | • | GND – 0.3V           |            | V <sub>CC</sub> + 0.3V | V     |

| V <sub>IN</sub>                               | Input Differential Voltage Range $(IN^+ - IN^-)$                               |                                                                                                           | • | -V <sub>REF</sub> /2 |            | V <sub>REF</sub> /2    | V     |

| REF <sup>+</sup>                              | Absolute/Common Mode REF <sup>+</sup> Voltage                                  |                                                                                                           |   | 0.1                  |            | V <sub>CC</sub>        | V     |

| REF <sup>-</sup>                              | Absolute/Common Mode REF <sup>-</sup> Voltage                                  |                                                                                                           | • | GND                  |            | $V_{CC} - 0.1V$        | V     |

| V <sub>REF</sub>                              | Reference Differential Voltage Range<br>(REF <sup>+</sup> – REF <sup>-</sup> ) |                                                                                                           | • | 0.1                  |            | V <sub>CC</sub>        | V     |

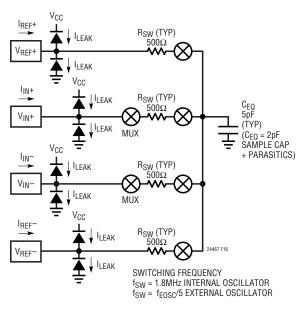

| C <sub>S(IN+)</sub>                           | IN <sup>+</sup> Sampling Capacitance                                           |                                                                                                           |   |                      | 2          |                        | pF    |

| C <sub>S(IN-)</sub>                           | IN <sup>-</sup> Sampling Capacitance                                           |                                                                                                           |   |                      | 2          |                        | pF    |

| C <sub>S(REF+)</sub>                          | REF <sup>+</sup> Sampling Capacitance                                          |                                                                                                           |   |                      | 2          |                        | pF    |

| C <sub>S(REF-)</sub>                          | REF <sup>-</sup> Sampling Capacitance                                          |                                                                                                           |   |                      | 2          |                        | pF    |

| I <sub>DC_LEAK(IN+, IN-,</sub><br>REF+, REF-) | Leakage Current, Inputs and Reference                                          | $\overline{CS} = V_{CC}$ , $IN^+ = GND$ , $IN^- = GND$ ,<br>REF <sup>+</sup> = 5V, REF <sup>-</sup> = GND | • | -15                  | 1          | 15                     | nA    |

| I <sub>SAMPLE(IN+, IN-,</sub><br>REF+, REF-)  | Average Input/Reference Current<br>During Sampling                             |                                                                                                           |   | Varies, See /        | Applicatio | ons Section            | nA    |

| t <sub>OPEN</sub>                             | MUX Break-Before-Make                                                          |                                                                                                           |   |                      | 50         |                        | ns    |

| QIRR                                          | MUX Off Isolation                                                              | V <sub>IN</sub> = 2V <sub>P-P</sub> DC to 1.8MHz                                                          |   |                      | 120        |                        | dB    |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL          | PARAMETER                                                       | CONDITIONS                                  |   | MIN                    | ТҮР | MAX  | UNITS |

|-----------------|-----------------------------------------------------------------|---------------------------------------------|---|------------------------|-----|------|-------|

| V <sub>IH</sub> | High Level Input Voltage CS, F <sub>0</sub>                     | $4.5V \le V_{CC} \le 5.5V$                  | • | 2.5                    |     |      | V     |

| V <sub>IL</sub> | Low Level Input Voltage $\overline{\text{CS}}$ , F <sub>0</sub> | $4.5V \le V_{CC} \le 5.5V$                  | • |                        |     | 0.8  | V     |

| V <sub>IH</sub> | High Level Input Voltage<br>SCK                                 | $4.5V \le V_{CC} \le 5.5V \text{ (Note 8)}$ | • | 2.5                    |     |      | V     |

| V <sub>IL</sub> | Low Level Input Voltage<br>SCK                                  | $4.5V \le V_{CC} \le 5.5V \text{ (Note 8)}$ | • |                        |     | 0.8  | V     |

| I <sub>IN</sub> | Digital Input Current<br>CS, F <sub>0</sub> , EXT, SOI          | $0V \le V_{IN} \le V_{CC}$                  | • | -10                    |     | 10   | μA    |

| I <sub>IN</sub> | Digital Input Current<br>SCK                                    | $0V \le V_{IN} \le V_{CC}$ (Note 8)         | • | -10                    |     | 10   | μA    |

| C <sub>IN</sub> | Digital Input Capacitance<br>CS, F <sub>0</sub>                 |                                             |   |                        | 10  |      | pF    |

| C <sub>IN</sub> | Digital Input Capacitance<br>SCK                                | (Note 8)                                    |   |                        | 10  |      | pF    |

| V <sub>OH</sub> | High Level Output Voltage<br>SDO, BUSY                          | I <sub>0</sub> = -800μA                     | • | V <sub>CC</sub> – 0.5V |     |      | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SDO, BUSY                           | I <sub>0</sub> = 1.6mA                      | • |                        |     | 0.4V | V     |

| V <sub>OH</sub> | High Level Output Voltage<br>SCK                                | I <sub>0</sub> = -800μA (Note 9)            | • | $V_{CC} - 0.5V$        |     |      | V     |

| V <sub>OL</sub> | Low Level Output Voltage<br>SCK                                 | I <sub>0</sub> = 1.6mA (Note 9)             | • |                        |     | 0.4V | V     |

| I <sub>OZ</sub> | Hi-Z Output Leakage<br>SDO                                      |                                             | • | -10                    |     | 10   | μA    |

# **POWER REQUIREMENTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL          | PARAMETER                                       | CONDITIONS                                                                                               |   | MIN | ТҮР    | MAX      | UNITS    |

|-----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|---|-----|--------|----------|----------|

| V <sub>CC</sub> | Supply Voltage                                  |                                                                                                          |   | 4.5 |        | 5.5      | V        |

|                 | Supply Current<br>Conversion Mode<br>Sleep Mode | $\frac{\overline{CS}}{\overline{CS}} = 0V \text{ (Note 7)}$<br>$\overline{CS} = V_{CC} \text{ (Note 7)}$ | • |     | 8<br>8 | 11<br>30 | mA<br>μA |

**TIMING CHARACTERISTICS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL            | PARAMETER                           | CONDITIONS                                                        |   | MIN         | ТҮР                                          | MAX         | UNITS     |

|-------------------|-------------------------------------|-------------------------------------------------------------------|---|-------------|----------------------------------------------|-------------|-----------|

| f <sub>EOSC</sub> | External Oscillator Frequency Range |                                                                   | • | 0.1         |                                              | 20          | MHz       |

| t <sub>HEO</sub>  | External Oscillator High Period     |                                                                   | • | 25          |                                              | 10000       | ns        |

| t <sub>LEO</sub>  | External Oscillator Low Period      |                                                                   | • | 25          |                                              | 10000       | ns        |

| t <sub>CONV</sub> | Conversion Time                     | OSR = 256<br>OSR = 32768                                          | • | 0.99<br>126 | 1.13<br>145                                  | 1.33<br>170 | ms<br>ms  |

|                   |                                     | External Oscillator (Notes 10, 13)                                | • | 4           | <u>40 ● OSR +1</u><br>f <sub>EOSC</sub> (kHz |             | ms        |

| f <sub>ISCK</sub> | Internal SCK Frequency              | Internal Oscillator (Note 9)<br>External Oscillator (Notes 9, 10) | • | 0.8         | 0.9<br>f <sub>EOSC</sub> /10                 | 1           | MHz<br>Hz |

### TIMING CHARACTERISTICS

The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                 | PARAMETER                                                  | CONDITIONS                                                             |   | MIN  | TYP                           | MAX  | UNITS   |

|------------------------|------------------------------------------------------------|------------------------------------------------------------------------|---|------|-------------------------------|------|---------|

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle                                    | (Note 9)                                                               | • | 45   |                               | 55   | %       |

| f <sub>ESCK</sub>      | External SCK Frequency Range                               | (Note 8)                                                               | • |      |                               | 20   | MHz     |

| t <sub>LESCK</sub>     | External SCK Low Period                                    | (Note 8)                                                               | • | 25   |                               |      | ns      |

| t <sub>HESCK</sub>     | External SCK High Period                                   | (Note 8)                                                               | • | 25   |                               |      | ns      |

| t <sub>DOUT_ISCK</sub> | Internal SCK 32-Bit Data Output Time                       | Internal Oscillator (Notes 9, 11)<br>External Oscillator (Notes 9, 10) | • | 41.6 | 35.3<br>320/f <sub>EOSC</sub> | 30.9 | μs<br>s |

| t <sub>DOUT_ESCK</sub> | External SCK 32-Bit Data Output Time                       | (Note 8)                                                               | • |      | 32/f <sub>ESCK</sub>          |      | S       |

| t <sub>1</sub>         | $\overline{CS} \downarrow$ to SDO Low Z                    | (Note 12)                                                              | • | 0    |                               | 25   | ns      |

| t <sub>2</sub>         | CS ↑ to SDO High Z                                         | (Note 12)                                                              | • | 0    |                               | 25   | ns      |

| t <sub>3</sub>         | $\overline{\text{CS}} \downarrow \text{to SCK} \downarrow$ | (Note 9)                                                               |   |      | 5                             |      | μS      |

| t <sub>4</sub>         | $\overline{\text{CS}} \downarrow \text{to SCK} \uparrow$   | (Notes 8, 12)                                                          | • | 25   |                               |      | ns      |

| t <sub>KQMAX</sub>     | SCK $\downarrow$ to SDO Valid                              |                                                                        | • |      |                               | 25   | ns      |

| t <sub>kqmin</sub>     | SDO Hold After SCK $\downarrow$                            | (Note 5)                                                               |   | 15   |                               |      | ns      |

| t <sub>5</sub>         | SCK Setup Before $\overline{\text{CS}} \downarrow$         |                                                                        | • | 50   |                               |      | ns      |

| t <sub>6</sub>         | SCK Hold After $\overline{\text{CS}} \downarrow$           |                                                                        | • |      |                               | 50   | ns      |

| t <sub>7</sub>         | SDI Setup Before SCK ↑                                     | (Note 5)                                                               | • | 10   |                               |      | ns      |

| t <sub>8</sub>         | SDI Hold After SCK ↑                                       | (Note 5)                                                               | • | 10   |                               |      | ns      |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2: All voltage values are with respect to GND.

Note 3:  $V_{CC} = 4.5V$  to 5.5V unless otherwise specified.

$V_{REF} = REF^+ - REF^-$ ,  $V_{REFCM} = (REF^+ + REF^-)/2$ ; REF<sup>+</sup> is the positive reference input, REF<sup>-</sup> is the negative reference input;  $V_{IN} = IN^+ - IN^-$ ,  $V_{INCM} = (IN^+ + IN^-)/2.$

Note 4: F<sub>0</sub> pin tied to GND or to external conversion clock source with

fEOSC = 10MHz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

**Note 6:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

### **PIN FUNCTIONS**

GND (Pins 1, 4, 5, 6, 31, 32, 33): Ground. Multiple ground pins internally connected for optimum ground current flow and V<sub>CC</sub> decoupling. Connect each one of these pins to a common ground plane through a low impedance connection. All seven pins must be connected to ground for proper operation.

BUSY (Pin 2): Conversion in Progress Indicator. This pin is HIGH while the conversion is in progress and goes LOW indicating the conversion is complete and data is ready. It remains LOW during the sleep and data output states. At the conclusion of the data output state, it goes HIGH indicating a new conversion has begun.

Note 7: The converter uses the internal oscillator.

Note 8: The converter is in external SCK mode of operation such that the SCK pin is used as a digital input. The frequency of the clock signal driving SCK during the data output is f<sub>FSCK</sub> and is expressed in Hz.

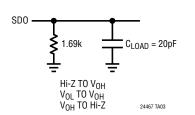

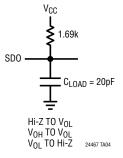

**Note 9:** The converter is in internal SCK mode of operation such that the SCK pin is used as a digital output. In this mode of operation, the SCK pin has a total equivalent load capacitance of  $C_{LOAD} = 20 pF$ .

Note 10: The external oscillator is connected to the  $F_0$  pin. The external oscillator frequency, f<sub>EOSC</sub>, is expressed in Hz.

**Note 11:** The converter uses the internal oscillator.  $F_0 = 0V$ .

Note 12: Guaranteed by design and test correlation.

Note 13: There is an internal reset that adds an additional 1µs (typ) to the conversion time.

EXT (Pin 3): Internal/External SCK Selection Pin. This pin is used to select internal or external SCK for outputting/ inputting data. If EXT is tied low, the device is in the external SCK mode and data is shifted out of the device under the control of a user applied serial clock. If EXT is tied high, the internal serial clock mode is selected. The device generates its own SCK signal and outputs this on the SCK pin. A framing signal BUSY (Pin 2) goes low indicating data is being output.

**COM (Pin 7):** The common negative input (IN<sup>-</sup>) for all single ended multiplexer configurations. The voltage on CHO-CH7 and COM pins can have any value between GND

### PIN FUNCTIONS

– 0.3V to V<sub>CC</sub> + 0.3V. Within these limits, the two selected inputs (IN<sup>+</sup> and IN<sup>-</sup>) provide a bipolar input range (V<sub>IN</sub> = IN<sup>+</sup>–IN<sup>-</sup>) from –0.5 • V<sub>REF</sub> to 0.5 • V<sub>REF</sub>. Outside this input range, the converter produces unique over-range and under-range output codes.

**CHO to CH7 (Pins 8, 9, 12, 13, 16, 17, 20, 21):** Analog Inputs. May be programmed for Single-ended or Differential mode.

$V_{REF01}^+$  (Pin 11),  $V_{REF01}^-$  (Pin 10)  $V_{REF23}^+$  (Pin 15),  $V_{REF23}^-$  (Pin 14),  $V_{REF45}^+$  (Pin 19),  $V_{REF45}^-$  (Pin 18),  $V_{REF67}^+$  (Pin 23),  $V_{REF67}^-$  (Pin 22): Differential Reference Inputs. The voltage on these pins can be anywhere between 0V and  $V_{CC}$  as long as the positive reference input ( $V_{EF01}^+$ ,  $V_{REF23}^+$ ,  $V_{REF45}^+$ ,  $V_{REF67}^+$ ) is greater than the corresponding negative reference input ( $V_{REF01}^-$ ,  $V_{REF23}^-$ ,  $V_{REF45}^-$ ,  $V_{REF67}^-$ ) by at least 100mV.

**NC (Pins 24, 25, 26, 27):** LTC2446 No Connect. These pins can either be tied to ground or left floating.

**MUXOUTP (Pin 24):** LTC2447 Positive Input Channel Multiplexer Output. Used to drive the input to an external buffer/amplifier for the selected positive input signal (IN<sup>+</sup>).

**ADCINP (Pin 25):** LTC2447 Positive ADC Input. Tie to output of buffer/amplifier driven by MUXOUTP.

**ADCINN (Pin 26):** LTC2447 Negative ADC Input. Tie to output of buffer/amplifier driven by MUXOUTN.

**MUXOUTN (Pin 27):** LTC2447 Negative Input Channel Multiplexer Output. Used to drive the input to an external buffer/amplifier for the selected negative input signal (IN<sup>-</sup>).

$V_{CC}$  (Pin 28): Positive Supply Voltage. Bypass to GND with a 10 $\mu$ F tantalum capacitor in parallel with a 0.1 $\mu$ F ceramic capacitor as close to the part as possible.

**V<sub>REFG</sub><sup>+</sup>** (**Pin 29**), **V<sub>REFG</sub><sup>-</sup>** (**Pin 30**): Global Reference Input. This differential reference input can be used for any input channel selected through a single bit in the digital input word.

**SDI (Pin 34):** Serial Data Input. This pin is used to select the speed, 1x or 2x mode, resolution, input channel and reference input for the next conversion cycle. At initial power-up, the default mode of operation is CH0-CH1,  $V_{REF01}$ , OSR of 256, and 1x mode. The serial data input

contains an enable bit which determines if a new channel/ speed is selected. If this bit is low the following conversion remains at the same speed and selected channel. The serial data input is applied to the device under control of the serial clock (SCK) during the data output cycle. The first conversion following a new channel/speed is valid.

**F**<sub>0</sub> (Pin 35): Frequency Control Pin. Digital input that controls the internal conversion clock. When F<sub>0</sub> is connected to V<sub>CC</sub> or GND, the converter uses its internal oscillator running at 9MHz. The conversion rate is determined by the selected OSR such that  $t_{CONV}$  (ms) = (40 • OSR + 170)/f<sub>OSC</sub> (kHz). The first digital filter null is located at 8/t<sub>CONV</sub>, 7kHz at OSR = 256 and 55Hz (Simultaneous 50/60Hz) at OSR = 32768. This pin may be driven with a maximum external clock of 10.24MHz resulting in a maximum 8kHz output rate (OSR = 64, 2x Mode).

**CS** (Pin 36): Active Low Chip Select. A LOW on this pin enables the SDO digital output and wakes up the ADC. Following each conversion the ADC automatically enters the sleep mode and remains in this low power state as long as CS is HIGH. A LOW-to-HIGH transition on CS during the Data Output aborts the data transfer and starts a new conversion.

**SDO (Pin 37):** Three-State Digital Output. During the data output period, this pin is used as serial data output. When the chip select  $\overline{CS}$  is HIGH ( $\overline{CS} = V_{CC}$ ) the SDO pin is in a high impedance state. During the conversion and sleep periods, this pin is used as the conversion status output. The conversion status can be observed by pulling  $\overline{CS}$  LOW. This signal is HIGH while the conversion is in progress and goes LOW once the conversion is complete.

**SCK (Pin 38):** Bidirectional Digital Clock Pin. In internal serial clock operation mode, SCK is used as a digital output for the internal serial interface clock during the data output period. In the external serial clock operation mode, SCK is used as the digital input for the external serial interface clock during the data output period. The serial clock operation mode is determined by the logic level applied to the EXT pin.

**Exposed Pad (Pin 39):** Ground. The exposed pad on the bottom of the package must be soldered to the PCB ground. For Prototyping purposes, this pin may remain floating.

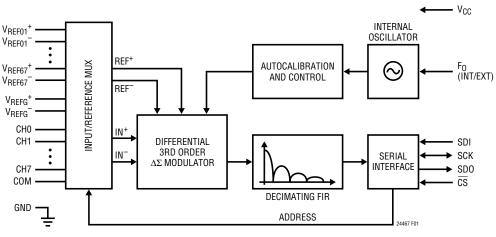

### FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

### **TEST CIRCUITS**

### **APPLICATIONS INFORMATION**

**CONVERTER OPERATION**

#### **Converter Operation Cycle**

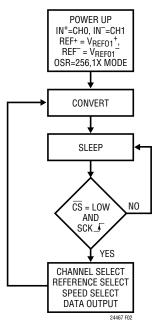

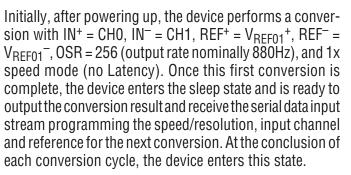

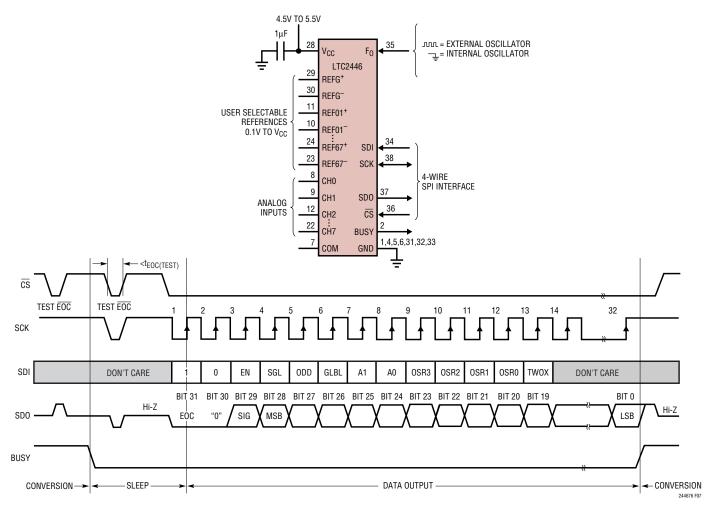

The LTC2446/LTC2447 are multichannel, multireference high speed, delta-sigma analog-to-digital converters with an easy to use 3- or 4-wire serial interface (see Figure 1). Their operation is made up of three states. The converter operating cycle begins with the conversion, followed by the low power sleep state and ends with the data output/ input (see Figure 2). The 4-wire interface consists of serial data input (SDI), serial data output (SDO), serial clock (SCK) and chip select ( $\overline{CS}$ ). The interface, timing, operation cycle and data out format is compatible with Linear's entire family of  $\Delta\Sigma$  converters.

Initially, the LTC2446/LTC2447 perform a conversion. Once the conversion is complete, the device enters the

Figure 2. LTC2446/LTC2447 State Transition Diagram 24467fa

sleep state. While in this sleep state, power consumption is reduced below  $10\mu$ A. The part remains in the sleep state as long as  $\overline{CS}$  is HIGH. The conversion result is held indefinitely in a static shift register while the converter is in the sleep state.

Once  $\overline{\text{CS}}$  is pulled LOW, the device begins outputting the conversion result. There is no latency in the conversion result while operating in the 1x mode. The data output corresponds to the conversion just performed. This result is shifted out on the serial data out pin (SDO) under the control of the serial clock (SCK). Data is updated on the falling edge of SCK allowing the user to reliably latch data on the rising edge of SCK (see Figure 3). The data output state is concluded once 32 bits are read out of the ADC or when  $\overline{\text{CS}}$  is brought HIGH. The device automatically initiates a new conversion and the cycle repeats.

Through timing control of the  $\overline{CS}$ , SCK and  $\overline{EXT}$  pins, the LTC2446/LTC2447 offer several flexible modes of operation (internal or external SCK). These various modes do not require programming configuration registers; moreover, they do not disturb the cyclic operation described above. These modes of operation are described in detail in the Serial Interface Timing Modes section.

### Ease of Use

The LTC2446/LTC2447 data output has no latency, filter settling delay or redundant data associated with the conversion cycle while operating in the 1x mode. There is a one-to-one correspondence between the conversion and the output data. Therefore, multiplexing multiple analog voltages and references is easy. Speed/resolution adjustments may be made seamlessly between two conversions without settling errors.

The LTC2446/LTC2447 perform offset and full-scale calibrations every conversion cycle. This calibration is transparent to the user and has no effect on the cyclic operation described above. The advantage of continuous calibration is extreme stability of offset and full-scale readings with respect to time, supply voltage change and temperature drift.

### **Power-Up Sequence**

The LTC2446/LTC2447 automatically enter an internal reset state when the power supply voltage  $V_{CC}\xspace$  drops

below approximately 2.2V. This feature guarantees the integrity of the conversion result and of the serial interface mode selection.

When the V<sub>CC</sub> voltage rises above this critical threshold, the converter creates an internal power-on-reset (POR) signal with a duration of approximately 0.5ms. The POR signal clears all internal registers. The conversion immediately following a POR is performed on the input channel  $IN^+ = CH0$ ,  $IN^- = CH1$ ,  $REF^+ = V_{REF01}^+$ ,  $REF^- V_{REF01}^-$  at an OSR = 256 in the 1x mode. Following the POR signal, the LTC2446/LTC2447 start a normal conversion cycle and follow the succession of states described above. The first conversion result following POR is accurate within the specifications of the device if the power supply voltage is restored within the operating range (4.5V to 5.5V) before the end of the POR time interval.

#### **Reference Voltage Range**

These converters accept truly differential external reference voltages. Each set of five reference inputs may be independently driven to any common mode voltage over the entire supply range of the device (GND to  $V_{CC}$ ). For correct converter operation, each positive reference pin REF<sup>+</sup> ( $V_{REF01}^+$ ,  $V_{REF23}^+$ ,  $V_{REF45}^+$ ,  $V_{REF67}^+$ ,  $V_{REFG}^+$ ) must be more positive than its corresponding negative reference pin REF<sup>-</sup> ( $V_{REF01}^-$ ,  $V_{REF01}^-$ ,  $V_{REF45}^-$ ,  $V_{REF67}^-$ ,  $V_{REF67}^-$ ) by at least 100mV.

The LTC2446/LTC2447 can accept a differential reference from 0.1V to  $V_{CC}$  on each set of reference input pins. The converter output noise is determined by the thermal noise of the front-end circuits, and as such, its value in microvolts is nearly constant with reference voltage. A decrease in reference voltage will not significantly improve the converter's effective resolution. On the other hand, a reduced reference voltage will improve the converter's overall INL performance.

#### **Input Voltage Range**

The analog input is truly differential with an absolute/ common mode range for the CH0-CH7 and COM input pins extending from GND – 0.3V to  $V_{CC}$  + 0.3V. Outside these limits, the ESD protection devices begin to turn on and the errors due to input leakage current increase rapidly. Within these limits, the LTC2446/LTC2447 24467ta

convert the bipolar differential input signal,  $V_{IN} = IN^+ - IN^-$  (where IN<sup>+</sup> and IN<sup>-</sup> are the selected input channels), from  $-FS = -0.5 \cdot V_{REF}$  to  $+FS = 0.5 \cdot V_{REF}$  where  $V_{REF} = REF^+ - REF^-$  (REF<sup>+</sup> and REF<sup>-</sup> are the selected references). Outside this range, the converter indicates the overrange or the underrange condition using distinct output codes.

#### MUXOUT/ADCIN

There are two differences between the LTC2446 and the LTC2447. The first is the RMS noise performance. For a given OSR, the LTC2447 noise level is approximately  $\sqrt{2}$  times lower (0.5 effective bits)than that of the LTC2446.

The second difference is the LTC2447 includes MUXOUT/ ADCIN pins. These pins enable an external buffer or gain block to be inserted between the selected input channel of the multiplexer and the input to the ADC. Since the buffer is driven by the output of the multiplexer, only one circuit is required for all 8 input channels. Additionally, the transparent calibration feature of the LTC244X family automatically removes the offset errors of the external buffer.

In order to achieve optimum performance, the MUXOUT and ADCIN pins should not be shorted together. In applications where the MUXOUT and ADCIN need to be shorted together, the LTC2446 should be used because the MUXOUT and ADCIN are internally connected for optimum performance.

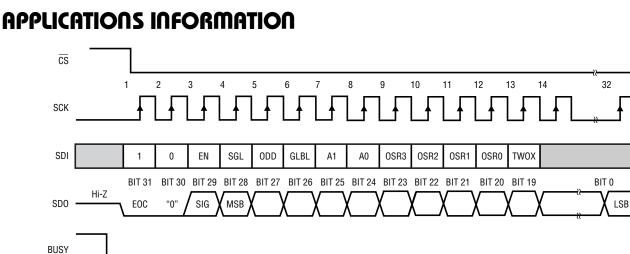

#### **Output Data Format**

The LTC2446/LTC2447 serial output data stream is 32 bits long. The first 3 bits represent status information indicating the sign and conversion state. The next 24 bits are the conversion result, MSB first. The remaining 5 bits are sub LSBs beyond the 24-bit level that may be included in averaging or discarded without loss of resolution. In the case of ultrahigh resolution modes, more than 24 effective bits of performance are possible (see Table 4). Under these conditions, sub LSBs are included in the conversion result and represent useful information beyond the 24-bit level. The third and fourth bit together are also used to indicate an underrange condition (the differential input voltage is below –FS) or an overrange condition (the differential input voltage is above +FS). Bit 31 (first output bit) is the end of conversion ( $\overline{EOC}$ ) indicator. This bit is available at the SDO pin during the conversion and sleep states whenever the  $\overline{CS}$  pin is LOW. This bit is HIGH during the conversion and goes LOW when the conversion is complete.

Bit 30 (second output bit) is a dummy bit (DMY) and is always LOW.

Bit 29 (third output bit) is the conversion result sign indicator (SIG). If V<sub>IN</sub> is >0, this bit is HIGH. If V<sub>IN</sub> is <0, this bit is LOW.

Bit 28 (fourth output bit) is the most significant bit (MSB) of the result. This bit in conjunction with Bit 29 also provides the underrange or overrange indication. If both Bit 29 and Bit 28 are HIGH, the differential input voltage is above +FS. If both Bit 29 and Bit 28 are LOW, the differential input voltage is below –FS.

The function of these bits is summarized in Table 1.

#### Table 1. LTC2446/LTC2447 Status Bits

| INPUT RANGE                            | BIT 31<br>EOC | BIT 30<br>DMY | BIT 29<br>Sig | BIT 28<br>MSB |

|----------------------------------------|---------------|---------------|---------------|---------------|

| $V_{IN} \ge 0.5 \bullet V_{REF}$       | 0             | 0             | 1             | 1             |

| $0V \le V_{IN} < 0.5 \bullet V_{REF}$  | 0             | 0             | 1             | 0             |

| $-0.5 \bullet V_{REF} \le V_{IN} < 0V$ | 0             | 0             | 0             | 1             |

| $V_{IN} < -0.5 \bullet V_{REF}$        | 0             | 0             | 0             | 0             |

Bits 28-5 are the 24-bit conversion result MSB first.

Bit 5 is the least significant bit (LSB).

Bits 4-0 are sub LSBs below the 24-bit level. Bits 4-0 may be included in averaging or discarded without loss of resolution.

Data is shifted out of the SDO pin under control of the serial clock (SCK), see Figure 3. Whenever  $\overline{CS}$  is HIGH, SDO remains high impedance and SCK is ignored.

In order to shift the conversion result out of the device,  $\overline{CS}$  must first be driven LOW.  $\overline{EOC}$  is seen at the SDO pin of the device once  $\overline{CS}$  is pulled LOW.  $\overline{EOC}$  changes real time from HIGH to LOW at the completion of a conversion. This signal may be used as an interrupt for an external microcontroller. Bit 31 ( $\overline{EOC}$ ) can be captured on the first

Figure 3. SDI Speed/Resolution, Channel Selection, and Data Output Timing

rising edge of SCK. Bit 30 is shifted out of the device on the first falling edge of SCK. The final data bit (Bit 0) is shifted out on the falling edge of the 31st SCK and may be latched on the rising edge of the 32nd SCK pulse. On the falling edge of the 32nd SCK pulse. On the falling the initiation of a new conversion cycle. This bit serves as EOC (Bit 31) for the next conversion cycle. Table 2 summarizes the output data format.

As long as the voltage on the IN<sup>+</sup> and IN<sup>-</sup> pins is maintained within the -0.3V to (V<sub>CC</sub> + 0.3V) absolute maximum operating range, a conversion result is generated for any differential input voltage V<sub>IN</sub> from  $-FS = -0.5 \cdot V_{REF}$  to  $+FS = 0.5 \cdot V_{REF}$ . For differential input voltages greater than

+FS, the conversion result is clamped to the value corresponding to the +FS + 1LSB. For differential input voltages below -FS, the conversion result is clamped to the value corresponding to -FS - 1LSB.

#### **SERIAL INTERFACE PINS**

The LTC2446/LTC2447 transmit the conversion results and receive the start of conversion command through a synchronous 3- or 4-wire interface. During the conversion and sleep states, this interface can be used to assess the converter status and during the data output state it is used to read the conversion result and program the speed, resolution and input channel.

| Differential Input Voltage<br>V <sub>IN</sub> * | Bit 31<br>EOC | Bit 30<br>DMY | Bit 29<br>SIG | Bit 28<br>MSB | Bit 27 | Bit 26 | Bit 25 | <br>Bit O |

|-------------------------------------------------|---------------|---------------|---------------|---------------|--------|--------|--------|-----------|

| $V_{IN}^* \ge 0.5 \bullet V_{REF}^{**}$         | 0             | 0             | 1             | 1             | 0      | 0      | 0      | <br>0     |

| 0.5 • V <sub>REF</sub> ** – 1LSB                | 0             | 0             | 1             | 0             | 1      | 1      | 1      | <br>1     |

| 0.25 • V <sub>REF</sub> **                      | 0             | 0             | 1             | 0             | 1      | 0      | 0      | <br>0     |

| 0.25 • V <sub>REF</sub> ** – 1LSB               | 0             | 0             | 1             | 0             | 0      | 1      | 1      | <br>1     |

| 0                                               | 0             | 0             | 1             | 0             | 0      | 0      | 0      | <br>0     |

| -1LSB                                           | 0             | 0             | 0             | 1             | 1      | 1      | 1      | <br>1     |

| -0.25 • V <sub>REF</sub> **                     | 0             | 0             | 0             | 1             | 1      | 0      | 0      | <br>0     |

| -0.25 • V <sub>REF</sub> ** - 1LSB              | 0             | 0             | 0             | 1             | 0      | 1      | 1      | <br>1     |

| -0.5 • V <sub>REF</sub> **                      | 0             | 0             | 0             | 1             | 0      | 0      | 0      | <br>0     |

| $V_{IN}^* < -0.5 \bullet V_{REF}^{**}$          | 0             | 0             | 0             | 0             | 1      | 1      | 1      | <br>1     |

Table 2. LTC2446/LTC2447 Output Data Format

\*The differential input voltage  $V_{IN} = IN^+ - IN^-$ . \*\*The differential reference voltage  $V_{REF} = REF^+ - REF^-$ .

24467fa

Hi-Z

#### Serial Clock Input/Output (SCK)

The serial clock signal present on SCK (Pin 38) is used to synchronize the data transfer. Each bit of data is shifted out the SDO pin on the falling edge of the serial clock.

In the Internal SCK mode of operation, the SCK pin is an output and the LTC2446/LTC2447 create their own serial clock. In the External SCK mode of operation, the SCK pin is used as input. <u>The</u> internal or external SCK mode is selected by tying EXT (Pin 3) LOW for external SCK and HIGH for internal SCK.

#### Serial Data Output (SDO)

The serial data output pin, SDO (Pin 37), provides the result of the last conversion as a serial bit stream (MSB first) during the data output state. In addition, the SDO pin is used as an end of conversion indicator during the conversion and sleep states.

When  $\overline{CS}$  (Pin 36) is HIGH, the SDO driver is switched to a high impedance state. This allows sharing the serial interface with other devices. If  $\overline{CS}$  is LOW during the convert or sleep state, SDO will output EOC. If  $\overline{CS}$  is LOW during the conversion phase, the EOC bit appears HIGH on the SDO pin. Once the conversion is complete, EOC goes LOW. The device remains in the sleep state until the first rising edge of SCK occurs while  $\overline{CS} = LOW$ .

#### Chip Select Input (CS)

The active LOW chip select,  $\overline{CS}$  (Pin 36), is used to test the conversion status and to enable the data output transfer as described in the previous sections.

In addition, the  $\overline{\text{CS}}$  signal can be used to trigger a new conversion cycle before the entire serial data transfer has been completed. The LTC2446/LTC2447 will abort any serial data transfer in progress and start a new conversion cycle anytime a LOW-to-HIGH transition is detected at the  $\overline{\text{CS}}$  pin after the converter has entered the data output state.

#### Serial Data Input (SDI)

The serial data input (SDI, Pin 34) is used to select the speed/resolution input channel and reference of the LTC2446/LTC2447. SDI is programmed by a serial input data stream under the control of SCK during the data output cycle, see Figure 3.

In order to change the speed/resolution, reference or input channel, the first 3 bits shifted into the device are 101. This is compatible with the programming sequence of the LTC2414/LTC2418/LTC2444/LTC2445/LTC2448/ LTC2449. If the sequence is set to 000 or 100, the following input data is ignored (don't care) and the previously selected speed/resolution, channel and reference remain valid for the next conversion. Combinations other than 101, 100, and 000 of the 3 control bits should be avoided.

If the first 3 bits shifted into the device are 101, then the following 5 bits select the input channel/reference for the following conversion (see Table 3). The next 5 bits select the speed/resolution and mode 1x (no Latency) 2x (double output rate with one conversion latency), see Table 4. If these 5 bits are set to all 0's, the previous speed remains selected for the next conversion. This is useful in applications requiring a fixed output rate/resolution but need to change the input channel or reference. In this case, the timing and input sequence is compatible with the LTC2414/LTC2418.

When an update operation is initiated (the first 3 bits are 101) the next 5 bits are the channel/reference address. The first bit, SGL, determines if the input selection is differential (SGL = 0) or single-ended (SGL = 1). For SGL = 0, two adjacent channels can be selected to form a differential input. For SGL = 1, one of 8 channels is selected as the positive input. The negative input is COM for all single ended operations. The global V<sub>RFF</sub> bit (GLBL) is used to determine which reference is selected. GLBL = 0 selects the individual reference slaved to a given channel. Each set of channels has a corresponding differential input reference. If GLBL = 1, a global reference  $V_{RFFG}^+/V_{RFFG}^-$  is selected. The global reference input may be used for any input channel selected. Table 3 shows a summary of input/ reference selection. The remaining bits (ODD, A1, A0) determine which channel is selected.

#### Table 3. Channel Selection for the LTC2446/LTC2447

|     | MUX A        | DDRES | S  |    |     |     |     | CHA | NNEL | INPUT |     |     |     | REFERENCE INPUT  |      |                  |                  |                  |                  |                  |                  |                  |                  |

|-----|--------------|-------|----|----|-----|-----|-----|-----|------|-------|-----|-----|-----|------------------|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| SGL | ODD/<br>Sign | GLBL  | A1 | AO | 0   | 1   | 2   | 3   | 4    | 5     | 6   | 7   | сом | 01+              | 01-  | 23+              | 23-              | 45+              | 45-              | 67+              | 67-              | G+               | G-               |

| * 0 | 0            | 0     | 0  | 0  | IN+ | IN- |     |     |      |       |     |     |     | REF <sup>+</sup> | REF- |                  |                  |                  |                  |                  |                  |                  |                  |

| 0   | 0            | 0     | 0  | 1  |     |     | IN+ | IN- |      |       |     |     |     |                  |      | REF <sup>+</sup> | REF <sup>-</sup> |                  |                  |                  |                  |                  |                  |

| 0   | 0            | 0     | 1  | 0  |     |     |     |     | IN+  | IN-   |     |     |     |                  |      |                  |                  | REF <sup>+</sup> | REF <sup>-</sup> |                  |                  |                  |                  |

| 0   | 0            | 0     | 1  | 1  |     |     |     |     |      |       | IN+ | IN- |     |                  |      |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |                  |                  |

| 0   | 1            | 0     | 0  | 0  | IN- | IN+ |     |     |      |       |     |     |     | REF+             | REF- |                  |                  |                  |                  |                  |                  |                  |                  |

| 0   | 1            | 0     | 0  | 1  |     |     | IN- | IN+ |      |       |     |     |     |                  |      | REF+             | REF-             |                  |                  |                  |                  |                  |                  |

| 0   | 1            | 0     | 1  | 0  |     |     |     |     | IN-  | IN+   |     |     |     |                  |      |                  |                  | REF+             | REF-             |                  |                  |                  |                  |

| 0   | 1            | 0     | 1  | 1  |     |     |     |     |      |       | IN- | IN+ |     |                  |      |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |                  |                  |

| 1   | 0            | 0     | 0  | 0  | IN+ |     |     |     |      |       |     |     | IN- | REF+             | REF- |                  |                  |                  |                  |                  |                  |                  |                  |

| 1   | 0            | 0     | 0  | 1  |     |     | IN+ |     |      |       |     |     | IN- |                  |      | REF+             | REF-             |                  |                  |                  |                  |                  |                  |

| 1   | 0            | 0     | 1  | 0  |     |     |     |     | IN+  |       |     |     | IN- |                  |      |                  |                  | REF+             | REF-             |                  |                  |                  |                  |

| 1   | 0            | 0     | 1  | 1  |     |     |     |     |      |       | IN+ |     | IN- |                  |      |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |                  |                  |

| 1   | 1            | 0     | 0  | 0  |     | IN+ |     |     |      |       |     |     | IN- | REF <sup>+</sup> | REF- |                  |                  |                  |                  |                  |                  |                  |                  |

| 1   | 1            | 0     | 0  | 1  |     |     |     | IN+ |      |       |     |     | IN- |                  |      | REF <sup>+</sup> | REF-             |                  |                  |                  |                  |                  |                  |

| 1   | 1            | 0     | 1  | 0  |     |     |     |     |      | IN+   |     |     | IN- |                  |      |                  |                  | REF <sup>+</sup> | REF <sup>-</sup> |                  |                  |                  |                  |

| 1   | 1            | 0     | 1  | 1  |     |     |     |     |      |       |     | IN+ | IN- |                  |      |                  |                  |                  |                  | REF <sup>+</sup> | REF <sup>-</sup> |                  |                  |

| 0   | 0            | 1     | 0  | 0  | IN+ | IN- |     |     |      |       |     |     |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF <sup>-</sup> |

| 0   | 0            | 1     | 0  | 1  |     |     | IN+ | IN- |      |       |     |     |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 0   | 0            | 1     | 1  | 0  |     |     |     |     | IN+  | IN-   |     |     |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 0   | 0            | 1     | 1  | 1  |     |     |     |     |      |       | IN+ | IN- |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 0   | 1            | 1     | 0  | 0  | IN- | IN+ |     |     |      |       |     |     |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 0   | 1            | 1     | 0  | 1  |     |     | IN- | IN+ |      |       |     |     |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 0   | 1            | 1     | 1  | 0  |     |     |     |     | IN-  | IN+   |     |     |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 0   | 1            | 1     | 1  | 1  |     |     |     |     |      |       | IN- | IN+ |     |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 0            | 1     | 0  | 0  | IN+ |     |     |     |      |       |     |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 0            | 1     | 0  | 1  |     |     | IN+ |     |      |       |     |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 0            | 1     | 1  | 0  |     |     |     |     | IN+  |       |     |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 0            | 1     | 1  | 1  |     |     |     |     |      |       | IN+ |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 1            | 1     | 0  | 0  |     | IN+ |     |     |      |       |     |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 1            | 1     | 0  | 1  |     |     |     | IN+ |      |       |     |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 1            | 1     | 1  | 0  |     |     |     |     |      | IN+   |     |     | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

| 1   | 1            | 1     | 1  | 1  |     |     |     |     |      |       |     | IN+ | IN- |                  |      |                  |                  |                  |                  |                  |                  | REF <sup>+</sup> | REF-             |

\*Default at power up

|      |      |      |      |      |               | SION RATE         |                  |                  |                 |                 |       |         |

|------|------|------|------|------|---------------|-------------------|------------------|------------------|-----------------|-----------------|-------|---------|

|      |      |      |      |      | INTERNAL      |                   | RMS              | RMS              |                 |                 |       |         |

| OSR3 | OSR2 | OSR1 | OSRO | тwox | 9MHz<br>Clock | 10.24MHz<br>Clock | NOISE<br>LTC2446 | NOISE<br>LTC2447 | ENOB<br>LTC2446 | ENOB<br>LTC2447 | OSR   | LATENCY |

| 0    | 0    | 0    | 0    | 0    | OLUUK         | OLUUK             |                  |                  | peed/Resolu     |                 | 0311  | LAILNUI |

| 0    | 0    |      | 1    |      | 2 5 2 1/1 -   | 4kHz              |                  |                  |                 | 17              | 64    | None    |

|      | -    | 0    |      | 0    | 3.52kHz       |                   | 23µV             | 23µV             | 17              |                 | 64    | None    |

| 0    | 0    | 1    | 0    | 0    | 1.76kHz       | 2kHz              | 4.4μV            | 3.5µV            | 20.1            | 20.1            | 128   | None    |

| 0    | 0    | 1    | 1    | 0    | 880Hz         | 1kHz              | 2.8µV            | 2μV              | 20.8            | 21.3            | 256   | None    |

| 0    | 1    | 0    | 0    | 0    | 440Hz         | 500Hz             | 2μV              | 1.4µV            | 21.3            | 21.8            | 512   | None    |

| 0    | 1    | 0    | 1    | 0    | 220Hz         | 250Hz             | 1.4µV            | 1µV              | 21.8            | 22.4            | 1024  | None    |

| 0    | 1    | 1    | 0    | 0    | 110Hz         | 125Hz             | 1.1µV            | 750nV            | 22.1            | 22.9            | 2048  | None    |

| 0    | 1    | 1    | 1    | 0    | 55Hz          | 62.5Hz            | 720nV            | 510nV            | 22.7            | 23.4            | 4096  | None    |

| 1    | 0    | 0    | 0    | 0    | 27.5Hz        | 31.25Hz           | 530nV            | 375nV            | 23.2            | 24              | 8192  | None    |

| 1    | 0    | 0    | 1    | 0    | 13.75Hz       | 15.625Hz          | 350nV            | 250nV            | 23.8            | 24.4            | 16384 | None    |

| 1    | 1    | 1    | 1    | 0    | 6.875Hz       | 7.8125Hz          | 280nV            | 200nV            | 24.1            | 24.6            | 32768 | none    |

| 0    | 0    | 0    | 0    | 1    |               |                   | Keep             | Previous S       | peed/Resol      | ution           |       |         |

| 0    | 0    | 0    | 1    | 1    | 7.04kHz       | 8kHz              | 23µV             | 23µV             | 17              | 17              | 64    | 1 Cycle |

| 0    | 0    | 1    | 0    | 1    | 3.52kHz       | 4kHz              | 4.4µV            | 3.5µV            | 20.1            | 20.1            | 128   | 1 Cycle |

| 0    | 0    | 1    | 1    | 1    | 1.76kHz       | 2kHz              | 2.8µV            | 2μV              | 20.8            | 21.3            | 256   | 1 Cycle |

| 0    | 1    | 0    | 0    | 1    | 880Hz         | 1kHz              | 2μV              | 1.4µV            | 21.3            | 21.8            | 512   | 1 Cycle |

| 0    | 1    | 0    | 1    | 1    | 440Hz         | 500Hz             | 1.4µV            | 1μV              | 21.8            | 22.4            | 1024  | 1 Cycle |

| 0    | 1    | 1    | 0    | 1    | 220Hz         | 250Hz             | 1.1µV            | 750nV            | 22.1            | 22.9            | 2048  | 1 Cycle |

| 0    | 1    | 1    | 1    | 1    | 110Hz         | 125Hz             | 720nV            | 510nV            | 22.7            | 23.4            | 4096  | 1 Cycle |

| 1    | 0    | 0    | 0    | 1    | 55Hz          | 62.5Hz            | 530nV            | 375nV            | 23.2            | 24              | 8192  | 1 Cycle |

| 1    | 0    | 0    | 1    | 1    | 27.5Hz        | 31.25Hz           | 350nV            | 250nV            | 23.8            | 24.4            | 16384 | 1 Cycle |

| 1    | 1    | 1    | 1    | 1    | 13.75Hz       | 15.625Hz          | 280nV            | 200nV            | 24.1            | 24.6            | 32768 | 1 Cycle |

Table 4. LTC2446/LTC2447 Speed/Resolution Selection

#### **Speed Multiplier Mode**

In addition to selecting the speed/resolution, a speed multiplier mode is used to double the output rate while maintaining the selected resolution. The last bit of the 5-bit speed/resolution control word (TWOX, see Table 4) determines if the output rate is 1x (no speed increase) or 2x (double the selected speed).

While operating in the 1x mode, the device combines two internal conversions for each conversion result in order to remove the ADC offset. Every conversion cycle, the offset and offset drift are transparently calibrated greatly simplifying the user interface. The conversion result has no latency. The first conversion following a newly selected speed/resolution and/or input/reference is valid. This is identical to the operation of the LTC2440, LTC2444, LTC2445, LTC2448, LTC2449, LTC2414 and LTC2418.

While operating in the 2x mode, the device performs a running average of the last two conversion results. This automatically removes the offset and drift of the device while increasing the output rate by 2x. The resolution (noise) remains the same as the 1x mode. If a new channel/reference is selected, the conversion result is valid for all conversions after the first conversion (one cycle latency). If a new speed/resolution is selected, the first conversion result is valid but the resolution (noise) is a function of the running average. All subsequent conversion results are valid. If the mode is changed from either 1x to 2x or 2x to 1x without changing the resolution or channel, the first conversion result is valid.

If an external buffer/amplifier circuit is used for the LTC2447, the 2x mode can be used to increase the settling time of the amplifier between readings. While operating in the 2x mode, the multiplexer output (input to the external buffer/amplifier) is switched at the end of each conversion cycle. Prior to concluding the data out/in cycle, the analog multiplexer output is switched. This occurs at the end of

the conversion cycle (just prior to the data output cycle) for auto calibration. The time required to read the conversion enables more settling time for the external buffer/ amplifier. The offset/offset drift of the external amplifiers are automatically removed by the converter's auto calibration sequence for both the 1x and 2x speed modes.

While operating in the 1x mode, if a new input channel/ reference is selected the multiplexer is switched on the falling edge of the 14th SCK (once the complete data input word is programmed). The remaining data output sequence time can be used to allow the external buffer/ amplifier to settle.

#### BUSY

The BUSY output (Pin 2) is used to monitor the state of conversion, data output and sleep cycle. While the part is converting, the BUSY pin is HIGH. Once the conversion is complete, BUSY goes LOW indicating the conversion is complete and data out is ready. The part now enters the LOW power sleep state. BUSY remains LOW while data is shifted out of the device and SDI is shifted into the device. It goes HIGH at the conclusion of the data input/output cycle indicating a new conversion has begun. This rising edge may be used to flag the completion of the data read cycle.

#### SERIAL INTERFACE TIMING MODES

The LTC2446/LTC2447's 3- or 4-wire interface is SPI and MICROWIRE compatible. This interface offers several flexible modes of operation. These include internal/external serial clock, 3- or 4-wire I/O, single cycle conversion and autostart. The following sections describe each of these serial interface timing modes in detail. In all these cases, the converter can use the internal oscillator ( $F_0 = LOW$ ) or an external oscillator connected to the  $F_0$  pin. Refer to Table 5 for a summary.

| Table 5. LTC2446/LTC | 2447 Interface | Timing Modes |

|----------------------|----------------|--------------|

|----------------------|----------------|--------------|

| CONFIGURATION                                   | SCK<br>SOURCE | CONVERSION<br>CYCLE<br>CONTROL | DATA<br>Output<br>Control          | CONNECTION<br>AND<br>WAVEFORMS |

|-------------------------------------------------|---------------|--------------------------------|------------------------------------|--------------------------------|

| External SCK, Single Cycle Conversion           | External      | CS and SCK                     | $\overline{\text{CS}}$ and SCK     | Figures 4, 5                   |

| External SCK, 3-Wire I/O                        | External      | SCK                            | SCK                                | Figure 6                       |

| Internal SCK, Single Cycle Conversion           | Internal      | CS↓                            | $\overline{\mathtt{CS}}\downarrow$ | Figures 7, 8                   |

| Internal SCK, 3-Wire I/O, Continuous Conversion | Internal      | Continuous                     | Internal                           | Figure 9                       |

|                                                 |               |                                |                                    | 24                             |

# External Serial Clock, Single Cycle Operation (SPI/MICROWIRE Compatible)

This timing mode uses an external serial clock to shift out the conversion result and a  $\overline{CS}$  signal to monitor and control the state of the conversion cycle, see Figure 4.

The serial clock mode is selected by the  $\overline{\text{EXT}}$  pin. To select the external serial clock mode,  $\overline{\text{EXT}}$  must be tied low.

The serial data output pin (SDO) is Hi-Z as long as  $\overline{CS}$  is HIGH. At any time during the conversion cycle,  $\overline{CS}$  may be pulled LOW in order to monitor the state of the converter. While  $\overline{CS}$  is pulled LOW,  $\overline{EOC}$  is output to the SDO pin.  $\overline{EOC} = 1$  (BUSY = 1) while a conversion is in progress and  $\overline{EOC} = 0$  (BUSY = 0) if the device is in the sleep state. Independent of  $\overline{CS}$ , the device automatically enters the low power sleep state once the conversion is complete. When the device is in the sleep state ( $\overline{EOC} = 0$ ), its conversion result is held in an internal static shift register. The device remains in the sleep state until the first rising edge of SCK is seen. Data is shifted out the SDO pin on each falling edge of SCK. This enables external circuitry to latch the output on the rising edge of SCK and the last bit of the conversion result can be latched on the 32nd rising edge of SCK. On the 32nd falling edge of SCK, the device begins a new conversion. SDO goes HIGH ( $\overline{EOC} = 1$ ) and BUSY goes HIGH indicating a conversion is in progress.

At the conclusion of the data cycle,  $\overline{\text{CS}}$  may remain LOW and  $\overline{\text{EOC}}$  monitored as an end-of-conversion interrupt. Alternatively,  $\overline{\text{CS}}$  may be driven HIGH setting SDO to Hi-Z and BUSY monitored for the completion of a conversion.

As described above,  $\overline{CS}$  may be pulled LOW at any time in order to monitor the conversion status on the SDO pin.

Typically,  $\overline{CS}$  remains LOW during the data output state. However, the data output state may be aborted by pulling  $\overline{CS}$  HIGH anytime between the fifth falling edge and the 32nd falling edge of SCK, see Figure 5. On the rising edge of  $\overline{CS}$ , the device aborts the data output state and immediately initiates a new conversion. Thirteen serial input data bits are required in order to properly program the speed/resolution and input/reference channel. If the data output sequence is aborted prior to the 13th rising edge of SCK, the new input data is ignored, and the previously selected speed/resolution and channel are used for the next conversion cycle. This is useful for systems not requiring all 32 bits of output data, aborting an invalid conversion cycle or synchronizing the start of a conversion. If a new channel is being programmed, the rising edge of CS must come after the 14th falling edge of SCK in order to store the data input sequence.

Figure 5. External Serial Clock, Reduced Output Data Length

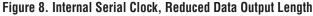

#### External Serial Clock, 3-Wire I/O

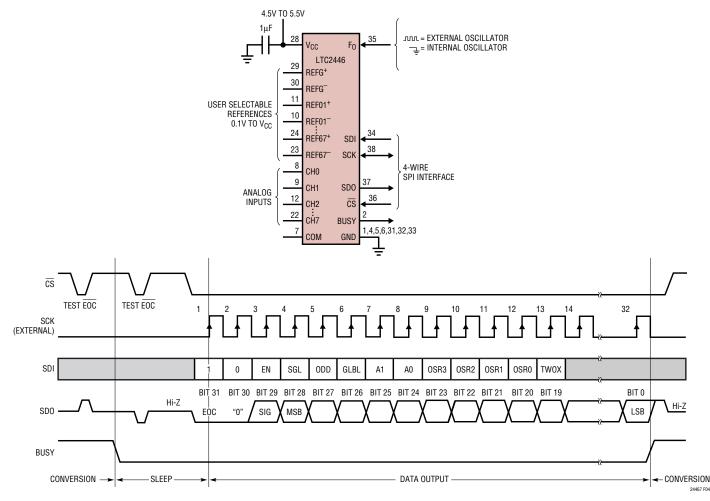

This timing mode utilizes a 3-wire serial I/O interface. The conversion result is shifted out of the device by an externally generated serial clock (SCK) signal, see Figure 6. CS may be permanently tied to ground, simplifying the user interface or isolation barrier. The external serial clock mode is selected by tying EXT LOW.

Since  $\overline{CS}$  is tied LOW, the end-of-conversion ( $\overline{EOC}$ ) can be continuously monitored at the SDO pin during the convert and sleep states. Conversely, BUSY (Pin 2) may be used to monitor the status of the conversion cycle. EOC or BUSY may be used as an interrupt to an external controller indicating the conversion result is ready. EOC = 1(BUSY = 1) while the conversion is in progress and EOC = 0 (BUSY = 0) once the conversion enters the low power sleep state. On the falling edge of EOC/BUSY, the conversion result is loaded into an internal static shift register. The device remains in the sleep state until the first rising edge of SCK. Data is shifted out the SDO pin on each falling edge of SCK enabling external circuitry to latch data on the rising edge of SCK. On the 32nd falling edge of SCK, SDO and BUSY go HIGH (EOC = 1) indicating a new conversion has begun.

Figure 6. External Serial Clock,  $\overline{CS} = 0$  Operation (3-Wire)

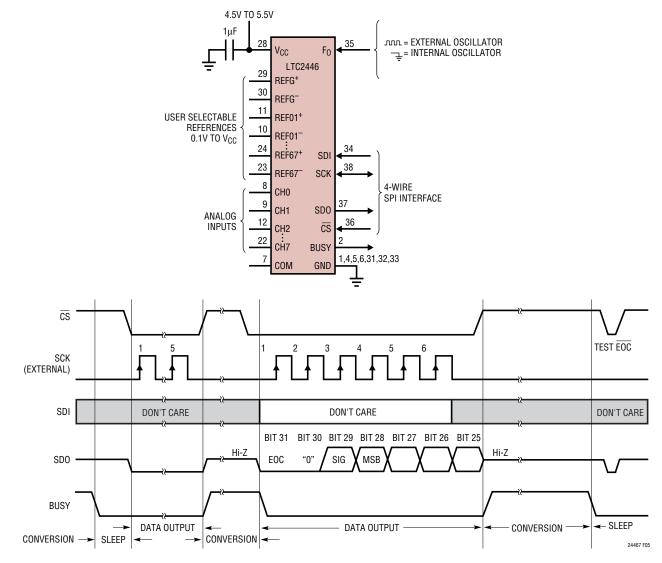

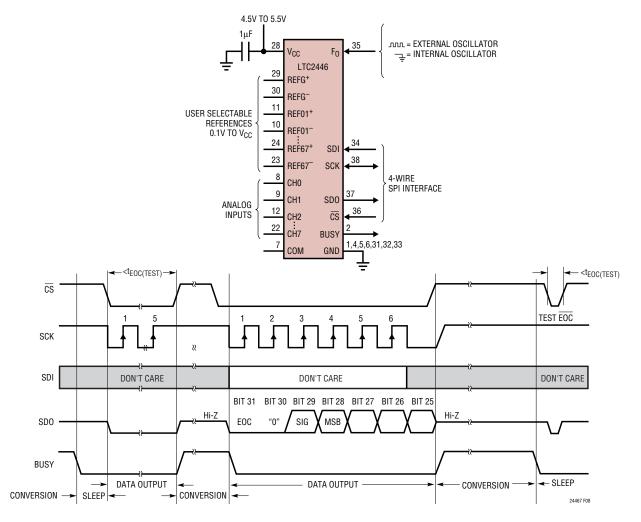

#### Internal Serial Clock, Single Cycle Operation

This timing mode uses an internal serial clock to shift out the conversion result and a  $\overline{CS}$  signal to monitor and control the state of the conversion cycle, see Figure 7.

In order to select the internal serial clock timing mode, the EXT pin must be tied HIGH.

The serial data output pin (SDO) is Hi-Z as long as  $\overline{CS}$  is HIGH. At any time during the conversion cycle,  $\overline{CS}$  may be pulled LOW in order to monitor the state of the converter. Once  $\overline{CS}$  is pulled LOW, SCK goes LOW and  $\overline{EOC}$  is output to the SDO pin.  $\overline{EOC} = 1$  while a conversion is in progress and  $\overline{EOC} = 0$  if the device is in the sleep state. Alternatively, BUSY (Pin 2) may be used to monitor the status of the conversion in progress. BUSY is HIGH during the conversion and goes LOW at the conclusion. It remains LOW until the result is read from the device.

When testing  $\overline{EOC}$ , if the conversion is complete ( $\overline{EOC} = 0$ ), the device will exit the sleep state and enter the data output state if  $\overline{CS}$  remains LOW. In order to prevent the device from exiting the low power sleep state,  $\overline{CS}$  must be pulled HIGH before the first rising edge of SCK. In the internal SCK timing mode, SCK goes HIGH and the device begins outputting data at time t<sub>EOCtest</sub> after the falling edge of  $\overline{CS}$  (if  $\overline{EOC} = 0$ ) or t<sub>EOCtest</sub> after  $\overline{EOC}$  goes LOW (if  $\overline{CS}$  is LOW during the falling edge of  $\overline{EOC}$ ). The value of t<sub>EOCtest</sub> is 500ns. If  $\overline{CS}$  is pulled HIGH before time t<sub>EOCtest</sub>, the device remains in the sleep state. The conversion result is held in the internal static shift register.

If  $\overline{\text{CS}}$  remains LOW longer than  $t_{\text{EOCtest}}$ , the first rising edge of SCK will occur and the conversion result is serially shifted out of the SDO pin. The data output cycle begins on this first rising edge of SCK and concludes after the 32nd rising edge. Data is shifted out the SDO pin on each falling edge of SCK. The internally generated serial clock is output to the SCK pin. This signal may be used to shift the conversion result into external circuitry. EOC can be latched on the first rising edge of SCK and the last bit of the conversion result on the 32nd rising edge of SCK. After the 32nd rising edge, SDO goes HIGH ( $\overline{EOC} = 1$ ), SCK stays HIGH and a new conversion starts.

Typically,  $\overline{\text{CS}}$  remains LOW during the data output state. However, the data output state may be aborted by pulling  $\overline{\text{CS}}$  HIGH anytime between the first and 32nd rising edge of SCK, see Figure 8. On the rising edge of  $\overline{CS}$ , the device aborts the data output state and immediately initiates a new conversion. This is useful for systems not requiring all 32 bits of output data, aborting an invalid conversion cycle, or synchronizing the start of a conversion. Thirteen serial input data bits are required in order to properly program the speed/resolution and input channel. If the data output sequence is aborted prior to the 13th rising edge of SCK, the new input data is ignored, and the previously selected speed/resolution and channel are used for the next conversion cycle. If a new channel is being programmed, the rising edge of  $\overline{CS}$  must come after the 14th falling edge of SCK in order to store the data input sequence.

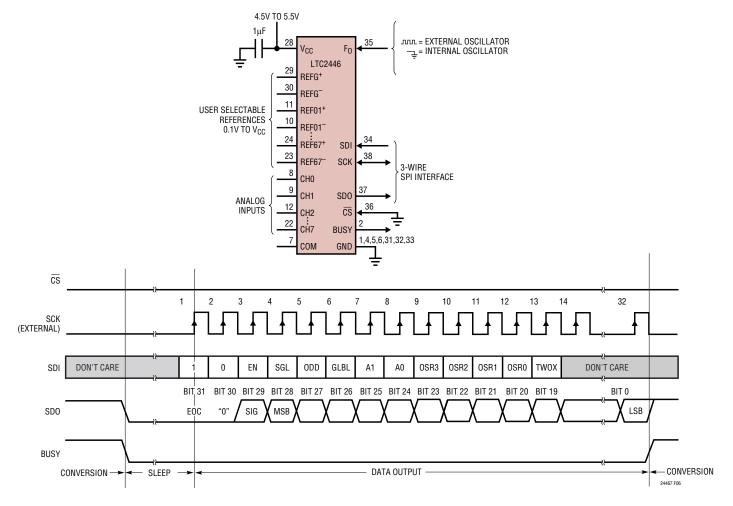

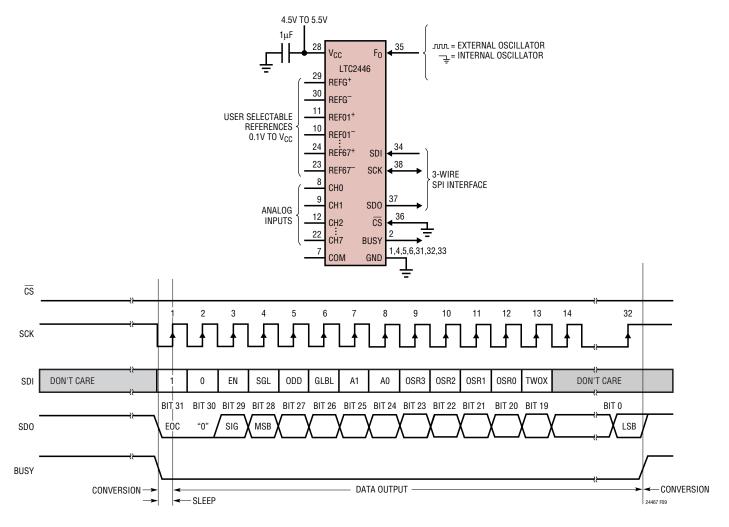

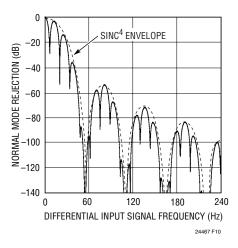

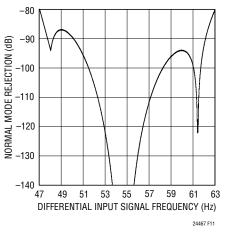

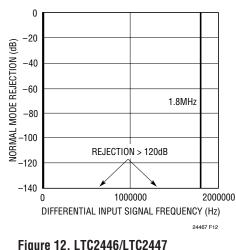

#### Internal Serial Clock, 3-Wire I/O, Continuous Conversion