25.03.2013

# History of Version

| Contents                                                                                                                      | Date                                                                                                      | Note                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| NEW VERSION                                                                                                                   | 20.04.2009                                                                                                | SPEC.                                                                                                         |

| UPDATE Quality Assurance 、Reliability<br>ADD Precautions for Handling 、Precautions for<br>Electrical 、Precautions for Storage | 25.03.2013                                                                                                |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               |                                                                                                           |                                                                                                               |

|                                                                                                                               | NEW VERSION<br>UPDATE Quality Assurance  < Reliability<br>ADD Precautions for Handling  < Precautions for | NEW VERSION20.04.2009UPDATE Quality Assurance < Reliability<br>ADD Precautions for Handling < Precautions for |

#### CONTENTS

- 1. Numbering System

- 2. General Specification

- 3. Absolute Maximum Rating

- 4. Electrical Characteristics

- 5. Optical Characteristics

- 6. Interface Pin Function

- 7. Power Supply For OLED Module And Panel Layout Diagram

- 8. Drawing

- 9. SSD1322controller data

- 9.1 Timing Characteristics

- 9.2 Display Control Instruction

- 9.3 Power ON / OFF Sequence & Application Circuit

- 10. Quality Assurance

- 10.1 Inspection conditions

- **10.2 Inspection Parameters**

- **10.3 WARRANTY POLICY**

- 10.4 MTBF

- 11. Reliability

- 12. Precautions for Handling

- 13. Precautions for Electrical

- 13.1 Design using the settings in the specification

- 13.2 Maximum Ratings

- 13.3 Power on/off procedure

- 13.4 Power savings

- 13.5 Residual Image (Image Sticking)

- 14. Precautions for Storage

# 1. Numbering System

# 2. General Specification

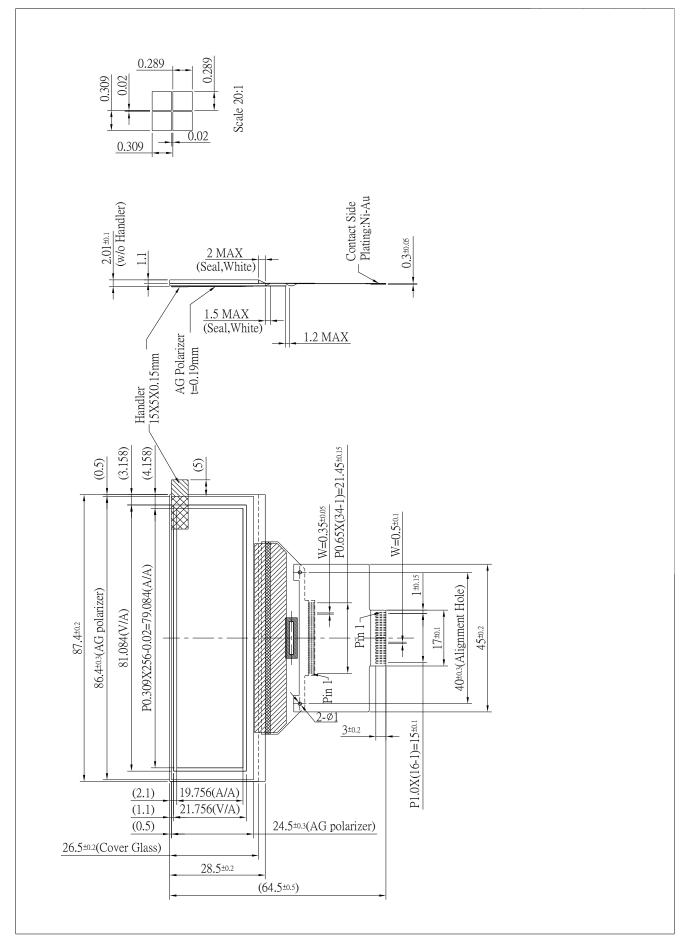

(1) Mechanical Dimension

| Item                     | Standard Value     | Unit |

|--------------------------|--------------------|------|

| Number of dots           | 256x64             | dots |

| Module dimension (L*W*H) | 87.4*64.5*2.01     | mm   |

| Active area              | 79.084*19.756      | mm   |

| Dot size                 | 0.289(W)×0.289(H)  | mm   |

| Dot pitch                | 0.309(W)×0.309 (H) | mm   |

| Color                    | Yellow             |      |

(2) Controller IC: SSD1322 Controller

(3) Temperature Range

| Operating | -40 ~ +70°C |

|-----------|-------------|

| Storage   | -40 ~ +85°C |

### 3. Absolute Maximum Ratings

| Item                     | Symbol | Condition                                 | Min      | Тур | Max | Unit |

|--------------------------|--------|-------------------------------------------|----------|-----|-----|------|

| Operating Temperature    | ТОР    |                                           | -40      |     | +70 | °C   |

| Storage Temperature      | TST    |                                           | -40      | _   | +85 | °C   |

| Humidity                 |        |                                           |          |     | 85  | %    |

| Supply Voltage For Logic | VDD    |                                           | 2.4      | _   | 3.5 | v    |

| Supply Voltage For Panel | VCC    |                                           | 10       |     | 20  |      |

| Operating lift time      |        | 100cd/m <sup>2</sup> , 50% checkerboard   | 24000(1) |     |     | Hrs  |

| Operating lift time      |        | 90cd/m <sup>2</sup> , 50%<br>checkerboard | 26000(2) |     |     | Hrs  |

| Operating lift time      |        | 80cd/m <sup>2</sup> , 50%<br>checkerboard | 30000(3) |     |     | Hrs  |

(A) Under VCC = 14.5V, Ta = 25°C, 50% RH.

(B) Life time is defined the amount of time when the luminance has decayed to less than 50% of the initial measured luminance.

| (1) Setting of 100 cd/m <sup>2</sup> : | Contrast setting : 0x74 | Frame rate : 105Hz | Duty setting : 1/64 |

|----------------------------------------|-------------------------|--------------------|---------------------|

| (2) Setting of 90 cd/m <sup>2</sup> :  | Contrast setting : 0x58 | Frame rate : 105Hz | Duty setting : 1/64 |

| (3) Setting of 80 cd/m <sup>2</sup> :  | Contrast setting : 0x4a | Frame rate : 105Hz | Duty setting: 1/64  |

# 4. Electrical Characteristics

| Item                             | Symbol                           | Condition | Min.        | Тур. | Max.               | Unit |

|----------------------------------|----------------------------------|-----------|-------------|------|--------------------|------|

| Supply Voltage For Logic         | V <sub>DD</sub> -V <sub>SS</sub> | _         | 2.4         | 3.3  | 3.5                | V    |

| Supply Voltage For Panel         | Vcc-V <sub>SS</sub>              | _         | 14          | 14.5 | 15                 | V    |

| Input High Vol                   | V <sub>IH</sub>                  | _         | $0.8V_{DD}$ | _    | V <sub>DD</sub>    | V    |

| Input Low Vol                    | V <sub>IL</sub>                  | _         | 0           | _    | $0.2V_{DD}$        | V    |

| Output High Vol                  | V <sub>OH</sub>                  |           | $0.9V_{DD}$ | _    | V <sub>DD</sub>    | V    |

| Output Low Vol.                  | V <sub>OL</sub>                  |           | 0           | _    | 0.1V <sub>DD</sub> | V    |

| Supply Current For Logic         |                                  |           |             |      |                    |      |

| (with built-in positive voltage) | I <sub>DD</sub>                  | _         | _           | 270  | _                  | mA   |

# 5. Optical Characteristics

| Item               | Min.   | Тур. | Max. | Unit |

|--------------------|--------|------|------|------|

| View Angle         | 160    | _    | _    | deg  |

| Dark Room contrast | 2000:1 | _    |      | _    |

| Response Time      | _      | 10   | —    | us   |

# 6. Interface Pin Function

| Pin No. | Symbol      | Level    | Description                                              |

|---------|-------------|----------|----------------------------------------------------------|

| 1       | Vss         | 0V       | Ground                                                   |

| 2       | Vdd         | 3.3V     | Supply voltage for logic                                 |

| 3       | CS          | H/L      | Chip select pin                                          |

| 4       | /RES        | H/L      | Hardware Reset pin                                       |

| 5       | D/C         | H/L      | H: Data; L: Command.                                     |

| 6       | WR          | H/L      | write signal pin                                         |

| 7       | RD          | H/L      | Read signal pin                                          |

| 8       | DB0         | H/L      | Data bus line                                            |

| 9       | DB1         | H/L      | Data bus line                                            |

| 10      | DB2         | H/L      | Data bus line                                            |

| 11      | DB3         | H/L      | Data bus line                                            |

| 12      | DB4         | H/L      | Data bus line                                            |

| 13      | DB5         | H/L      | Data bus line                                            |

| 14      | DB6         | H/L      | Data bus line                                            |

| 15      | DB7         | H/L      | Data bus line                                            |

| 16      | DISF<br>VCC | H/L<br>H | DISF: VCC Voltage ON/OFF<br>VCC: Supply Voltage For OLED |

#### Default: Parallel 8-Bit 8080 Interface 68j : Parallel 8-Bit 6800 Interface Special Code 20i : SPI Interface Special Code

#### MCU interface assignment under different bus interface mode

| Pin Name Data/Command Interface<br>Bus |            |        |    |    |      |      | Control Signal |      |       |              |      |                       |      |

|----------------------------------------|------------|--------|----|----|------|------|----------------|------|-------|--------------|------|-----------------------|------|

| Interface                              | <b>D</b> 7 | D6     | D5 | D4 | D3   | D2   | D1             | D0   | Ε     | <b>R/W</b> # | CS#  | <b>D</b> / <b>C</b> # | RES# |

| 8-bit 8080                             |            |        |    | D[ | 7:0] |      |                |      | RD#   | WR#          | CS#  | D/C#                  | RES# |

| 8-bit 6800                             |            | D[7:0] |    |    |      |      |                | E    | R/W#  | CS#          | D/C# | RES#                  |      |

| 3-wire SPI                             | Tie LOW    |        |    | NC | SDIN | SCLK | Tie L          | OW   | CS#   | Tie LOW      | RES# |                       |      |

| 4-wire SPI                             | Tie LO     | W      |    |    |      | NC   | SDIN           | SCLK | Tie L | .OW          | CS#  | D/C#                  | RES# |

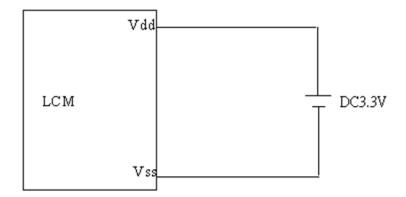

# 7. Power Supply For OLED Module And Panel Layout Diagram

OLED Module operating on "DC 3.3V " input with built-in positive voltage

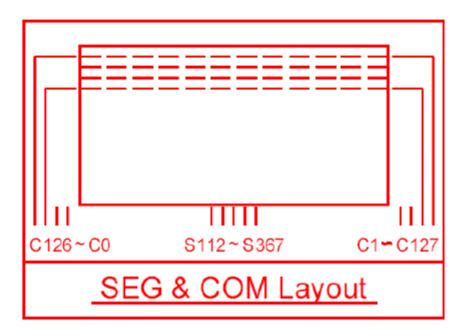

Panel Layout Diagram

# 8. Drawing

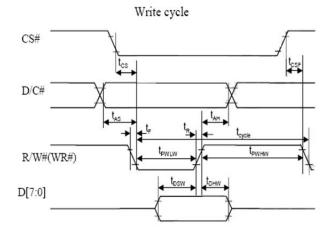

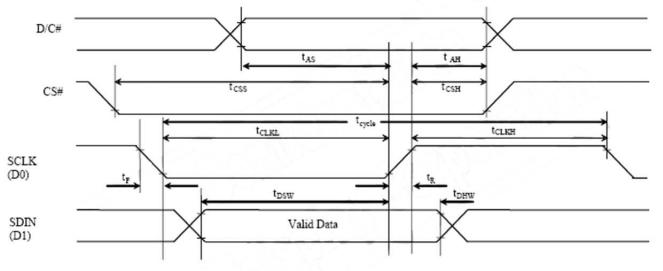

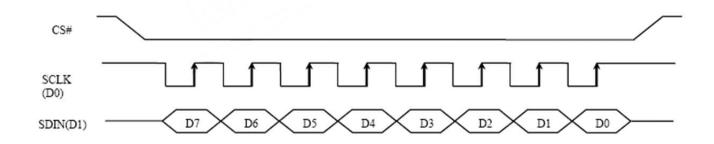

#### 9. SSD1322 controller data 9.1 Timing Characteristics .8080 MPU Interface

Fall Time

Chip select setup time

Chip select hold time

Chip select hold time to read signal

t<sub>R</sub>

t<sub>F</sub>

t<sub>cs</sub>

t<sub>CSH</sub>

t<sub>CSF</sub>

$(V_{DD} - V_{SS} = 2.4 \text{ to } 2.6 \text{V}, V_{DDIO} = 1.6 \text{V}, V_{CI} = 3.3 \text{V}, T_A = 25^{\circ}\text{C})$ Min Symbol Parameter Clock Cycle Time 300 t<sub>cycle</sub> Address Setup Time 10 t<sub>AS</sub> Address Hold Time 0  $t_{AH}$ Write Data Setup Time 40 t<sub>DSW</sub> Write Data Hold Time 7  $t_{\rm DHW}$ 20 Read Data Hold Time t<sub>DHR</sub> Output Disable Time t<sub>OH</sub> Access Time t<sub>ACC</sub> Read Low Time 150 tPWLR Write Low Time 60  $t_{\rm PWLW}$ Read High Time 60 t<sub>PWHR</sub> Write High Time 60 t<sub>PWHW</sub> Rise Time

#### 8080-series MCU parallel interface characteristics

Max

-

-

-

-

-

-

70

140

\_

-

-

-

15

15

-

-

-

Тур

-

-

-

\_

-

-

-

-

\_

-

-

-

-

-

-

-

\_

-

-

0

0

20

Unit

ns

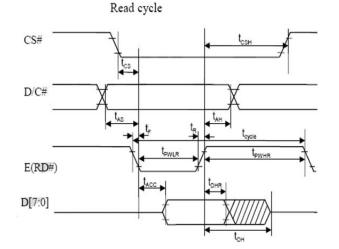

#### 6800 MPU Interface

| Symbol                       | Parameter                            | Min | Тур | Max | Unit |

|------------------------------|--------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub>           | Clock Cycle Time                     | 300 | -   | -   | ns   |

| t <sub>AS</sub>              | Address Setup Time                   | 10  | -   | -   | ns   |

| t <sub>AH</sub>              | Address Hold Time                    | 0   | -   | -   | ns   |

| t <sub>DSW</sub>             | Write Data Setup Time                | 40  | -   | -   | ns   |

| t <sub>DHW</sub>             | Write Data Hold Time                 | 7   | -   | -   | ns   |

| t <sub>DHR</sub>             | Read Data Hold Time                  | 20  | -   | -   | ns   |

| t <sub>OH</sub>              | Output Disable Time                  | -   | -   | 70  | ns   |

| t <sub>ACC</sub>             | Access Time                          | -   | -   | 140 | ns   |

|                              | Chip Select Low Pulse Width (read)   | 120 |     |     |      |

| $\mathrm{PW}_{\mathrm{CSL}}$ | Chip Select Low Pulse Width (write)  | 60  | -   | -   | ns   |

| DW                           | Chip Select High Pulse Width (read)  | 60  |     |     |      |

| $PW_{CSH}$                   | Chip Select High Pulse Width (write) | 60  | · _ | -   | ns   |

| t <sub>R</sub>               | Rise Time                            | -   | - / | 15  | ns   |

| t <sub>F</sub>               | Fall Time                            | - / | -   | 15  | ns   |

#### $(V_{DD} - V_{SS} = 2.4 \text{ to } 2.6 \text{V}, V_{DDIO} = 1.6 \text{V}, V_{CI} = 3.3 \text{V}, T_A = 25^{\circ}\text{C})$

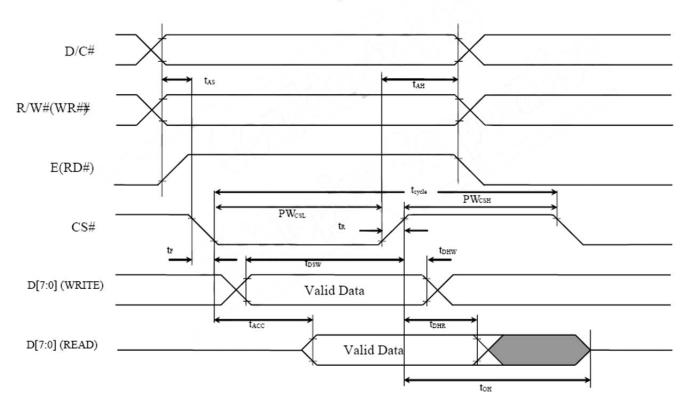

#### 6800-series MCU parallel interface characteristics

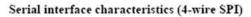

#### Serial Interface(4-wire SPI)

#### $(V_{\text{DD}}$ - $V_{\text{SS}}$ = 2.4 to 2.6V, $V_{\text{DDIO}}\text{=}1.6V, \, V_{\text{CI}}\text{=}3.3V, \, T_{\text{A}}\text{=}25^{\circ}\text{C})$

| Symbol             | Parameter              | Min | Тур | Max | Unit |

|--------------------|------------------------|-----|-----|-----|------|

| t <sub>cvcle</sub> | Clock Cycle Time       | 100 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 15  | -   | -   | ns   |

| t <sub>css</sub>   | Chip Select Setup Time | 20  | -   | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 10  | -   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 15  | -   | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 15  | -   | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 20  | -   | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 20  | -   | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | -   | 15  | ns   |

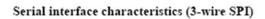

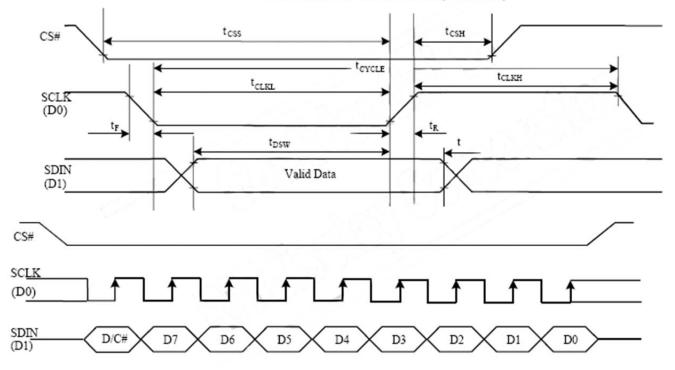

#### Serial Interface (3-wire SPI)

### (V\_DD - V\_SS = 2.4 to 2.6V, V\_DDIO=1.6V, V\_CI = 3.3V, T\_A = 25^{\circ}C)

| Symbol             | Parameter              | Min | Тур | Max | Unit |

|--------------------|------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 100 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time     | 15  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time      | 15  | -   | -   | ns   |

| tcss               | Chip Select Setup Time | 20  | -   | -   | ns   |

| tCSH               | Chip Select Hold Time  | 10  | -   | -   | ns   |

| tDSW               | Write Data Setup Time  | 15  | -   | -   | ns   |

| tDHW               | Write Data Hold Time   | 15  | -   | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 20  | -   | -   | ns   |

| tCLKH              | Clock High Time        | 20  | -   | -   | ns   |

| tR                 | Rise Time              | -   | -   | 15  | ns   |

| tF                 | Fall Time              | -   | -   | 15  | ns   |

|                    |                        |     |     |     |      |

# 9.2 Display Control Instruction

(D/C#=0, R/W#(WR#) = 0, E(RD#)=1) unless specific setting is stated)

| D/C#        | Hex                    | D7          | Dó                                    | D5                                    | D4            | D3                                    | D2                                    | D2                                    | D0                                    | Command                                 | Description                                                                                                                     |

|-------------|------------------------|-------------|---------------------------------------|---------------------------------------|---------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0           | 00                     | 0           | 0                                     | 0                                     | 0             | 0                                     | 0                                     | 0                                     | 0                                     |                                         | This command is sent to enable the Gray Scale table setting<br>(command B8h)                                                    |

| 0<br>1<br>1 | 15<br>A[6:0]<br>B[6:0] | 0<br>*<br>* | 0<br>A6<br>B6                         | 0<br>As<br>Bs                         | 1<br>A4<br>B4 | 0<br>A3<br>B3                         | 1<br>A2<br>B2                         | 0<br>A1<br>B1                         | 1<br>A <sub>0</sub><br>B <sub>0</sub> | Address                                 | Set Column start and end address<br>A[6:0]: Start Address. [reset=0]<br>B[6:0]: End Address. [reset=119]<br>Range from 0 to 119 |

| 0           | 5C                     | 0           | 1                                     | 0                                     | 1             | 1                                     | 1                                     | 0                                     | 0                                     | Write RAM<br>Command                    | Enable MCU to write Data into RAM                                                                                               |

| 0           | 5D                     | 0           | 1                                     | 0                                     | 1             | 1                                     | 1                                     | 0                                     | 1                                     | Read RAM<br>Command                     | Enable MCU to read Data from RAM                                                                                                |

| 0<br>1<br>1 | 75<br>A[6:0]<br>B[6:0] | 0<br>*<br>* | 1<br>A <sub>6</sub><br>B <sub>6</sub> | 1<br>A <sub>5</sub><br>B <sub>5</sub> | 1<br>A4<br>B4 | 0<br>A <sub>3</sub><br>B <sub>3</sub> | 1<br>A <sub>2</sub><br>B <sub>2</sub> | 0<br>A <sub>1</sub><br>B <sub>1</sub> | 1<br>A <sub>0</sub><br>B <sub>0</sub> | Address                                 | Set Row start and end address<br>A[6:0]: Start Address. [reset=0]<br>B[6:0]: End Address. [reset=127]<br>Range from 0 to 127    |

| 0 1 1       | A0<br>A[7:0]<br>B[4]   | 1 0 *       | 0 0 *                                 | 1<br>As<br>0                          | 0<br>A4<br>B4 | 000                                   | 0 A2 0                                | 0<br>A <sub>1</sub><br>0              | 0<br>A <sub>0</sub><br>1              | Set Re-map and<br>Dual COM Line<br>mode |                                                                                                                                 |

| 0           | A1<br>A[6:0]           | 1           | 0<br>A6                               | 1<br>Aş                               | 0<br>A4       | 0<br>A3                               | 0<br>A2                               | 0<br>A1                               | 1<br>A <sub>0</sub>                   |                                         | Set display RAM display start line register from 0-127<br>Display start line register is reset to 00h after RESET               |

| D/C# | Hex    | <b>D</b> 7 | D6                    | D5             | D4             | D3             | D2                    | D2               | D0             | Command                 | Description                                                                                |  |  |

|------|--------|------------|-----------------------|----------------|----------------|----------------|-----------------------|------------------|----------------|-------------------------|--------------------------------------------------------------------------------------------|--|--|

| 0    | A2     | 1          | 0                     | 1              | 0              | 0              | 0                     | 1                | 0              | 6 (D) 1                 |                                                                                            |  |  |

| 1    | A[6:0] | *          | $A_6$                 | A5             | A4             | $A_3$          | A <sub>2</sub>        | $A_1$            | A <sub>0</sub> |                         | Set vertical scroll by COM from 0-127<br>The value is reset to 00H after RESET             |  |  |

| 0    | A4~A7  | 1          | 0                     | 1              | 0              | 0              | X2                    | $X_1$            | X <sub>0</sub> |                         | A4h = Entire Display OFF, all pixels turns OFF in GS level 0                               |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | A5h = Entire Display ON, all pixels turns ON in GS level 15                                |  |  |

|      |        |            |                       |                |                |                |                       |                  |                | Set Display<br>Mode     | A6h = Normal Display [reset]                                                               |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | A7h = Inverse Display (GS0 → GS15, GS1 → GS14, GS2<br>→ GS13,)                             |  |  |

| 0    | A8     | 1          | 0                     | 1              | 0              | 1              | 0                     | 0                | 0              |                         | This command turns ON partial mode. The partial mode                                       |  |  |

| 1    | A[6:0] | 0          | A <sub>6</sub>        | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub>        | A <sub>1</sub>   | A <sub>0</sub> | Enable Partial          | display area is defined by the following two parameters,                                   |  |  |

| 1    | B[6:0] | 0          | <b>B</b> <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | <b>B</b> <sub>2</sub> | B1               | B <sub>0</sub> | Display                 | A[6:0]: Address of start row in the display area                                           |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | B[6:0]: Address of end row in the display area,<br>where B[6:0] must be ≥ A[6:0]           |  |  |

| 0    | A9     | 1          | 0                     | 1              | 0              | 1              | 0                     | 0                | 1              |                         | This command is cont to crit the Destin Direlay mode                                       |  |  |

| Ŭ    | R9     | 1          | v                     |                | Ŭ              | 1              | Ŭ                     | Ū                | 1              | Exit Partial<br>Display | This command is sent to exit the Partial Display mode                                      |  |  |

| 0    | AB     | 1          | 0                     | 1              | 0              | 1              | 0                     | 1                | 1              | Function                | A[0]=0b, Select external V <sub>DD</sub>                                                   |  |  |

| 1    | A[0]   | 0          | 0                     | 0              | 0              | 0              | 0                     | 0                | A <sub>0</sub> |                         | A[0]=1b, Enable internal V <sub>DD</sub> regulator [reset]                                 |  |  |

| 0    | AE~AF  | 1          | 0                     | 1              | 0              | 1              | 1                     | 1                | $\mathbf{X}_0$ | Cat Class made          | AEh = Sleep mode ON (Display OFF)<br>AFh = Sleep mode OFF (Display ON)                     |  |  |

|      |        |            |                       | /              |                |                |                       |                  |                |                         |                                                                                            |  |  |

| 0    | B1     | 1          | 0                     | 1              | 1              | 0              | 0                     | 0                | 1              |                         | A[3:0] Phase 1 period (reset phase length) of 5~31 DCLK(s)<br>clocks as follow:            |  |  |

| 1    | A[7:0] | A7         | A <sub>6</sub>        | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub>        | $A_1$            | A <sub>0</sub> | AVA).                   |                                                                                            |  |  |

|      |        |            |                       |                |                |                |                       | ~ S <sup>1</sup> | 20             |                         | A[3:0] Phase 1 period<br>0000 invalid                                                      |  |  |

|      |        |            |                       |                |                |                |                       | 20               |                | DN //                   | 0000 invalid                                                                               |  |  |

|      |        |            |                       |                |                | 60             |                       |                  | 1              |                         | 0010 5 DCLKs                                                                               |  |  |

|      |        |            |                       |                |                |                | $\sim$                |                  | 1              |                         | 0011 7 DCLKs<br>0100 9 DCLKs [reset]                                                       |  |  |

|      |        |            |                       |                |                |                | Ľ.,                   | 1                |                |                         | : :                                                                                        |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | 1111 31 DCLKs                                                                              |  |  |

|      |        |            |                       |                |                | $\sim$         |                       |                  |                |                         |                                                                                            |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | A[7:4] Phase 2 period (first pre-charge phase length) of<br>3~15 DCLK(s) clocks as follow: |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | A[7:4] Phase 2 period                                                                      |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | 0000 invalid                                                                               |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | 0001 invalid                                                                               |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | 0010 invalid<br>0011 3 DCLKs                                                               |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | : :                                                                                        |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | 0111 7 DCLKs [reset]                                                                       |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | : :<br>1111 15 DCLK5                                                                       |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         | ini ibictas                                                                                |  |  |

|      |        |            |                       |                |                |                |                       |                  |                |                         |                                                                                            |  |  |

| D/C#                            | Hex                                              | D7           | D6                                  | D5                       | D4                       | D3                       | D2          | D2                                  | D0                                                                              | Command                                                 | Description                                                                                                                                                                                                                                                                                   |  |

|---------------------------------|--------------------------------------------------|--------------|-------------------------------------|--------------------------|--------------------------|--------------------------|-------------|-------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                               | <b>B</b> 3                                       | 1            | 0                                   | 1                        | 1                        | 0                        | 0           | 1                                   | 1                                                                               |                                                         | A[3:0] [reset=0], divide by DIVSET where                                                                                                                                                                                                                                                      |  |

|                                 |                                                  |              |                                     |                          |                          |                          |             |                                     |                                                                                 | Set Front Clock<br>Divider /<br>Oscillator<br>Frequency | A[3:0]         [reset=0], divide by DIVSET where           A[3:0]         DIVSET           0000         divide by 1           0001         divide by 2           0010         divide by 4           0011         divide by 8           0100         divide by 1                               |  |

| 0<br>1<br>1                     | B4<br>A[1:0]<br>B[7:3]                           | 1<br>1<br>B7 | 0<br>0<br>B <sub>6</sub>            | 1<br>1<br>B <sub>5</sub> | 1<br>0<br>B <sub>4</sub> | 0<br>0<br>B <sub>3</sub> | 1<br>0<br>1 | 0<br>A <sub>1</sub><br>0            | 0<br>A <sub>0</sub><br>1                                                        | Display<br>Enhancement A                                | A[1:0] = 00b: Enable external VSL<br>A[1:0] = 10b: Internal VSL [reset]<br>B[7:3] = 11111b: Enhanced low GS display quality<br>B[7:3] = 10110b: Normal [reset]                                                                                                                                |  |

| 0                               | B5<br>A[3:0]                                     | 1 *          | 0<br>*                              | 1 *                      | 1 *                      | 0<br>A3                  | 1<br>A2     | 0<br>A1                             | 1<br>A <sub>0</sub>                                                             | Set GPIO                                                | A[1:0] GPIO0: 00 pin HiZ, Input disabled<br>01 pin HiZ, Input enabled<br>10 pin output LOW [reset]<br>11 pin output HIGH<br>A[3:2] GPIO1: 00 pin HiZ, Input disabled<br>01 pin HiZ, Input enabled<br>10 pin output LOW [reset]<br>11 pin output HIGH                                          |  |

| 0                               | B6<br>A[3:0]                                     | 1            | 0<br>*                              | 1 *                      | 1 *                      | 0<br>A3                  | 1<br>A2     | 1<br>A1                             | 0<br>A <sub>0</sub>                                                             | Set Second<br>Precharge<br>Period                       | A[3:0] Second Pre-charge period<br>0000b 0 dclk<br>0001b 1 dclk<br>1000b 8 dclks [reset]<br>1111b 15 dclks                                                                                                                                                                                    |  |

| 0<br>1<br>1<br>1<br>1<br>1<br>1 | B8<br>A1[7:0]<br>A2[7:0]<br>A14[7:0]<br>A15[7:0] | A2,<br>A14,  | A2 <sub>6</sub><br>A14 <sub>6</sub> |                          |                          | A23                      |             | A2 <sub>1</sub><br>A14 <sub>1</sub> | 0<br>Al <sub>0</sub><br>A2 <sub>0</sub><br>Al4 <sub>0</sub><br>Al5 <sub>0</sub> | Table                                                   | The next 15 data bytes define Gray Scale (GS) Table by<br>setting the gray scale pulse width in unit of DCLK's<br>(ranges from 0d ~ 180d)<br>A1[7:0]: Gamma Setting for GS1,<br>A2[7:0]: Gamma Setting for GS2,<br>:<br>A14[7:0]: Gamma Setting for GS14,<br>A15[7:0]: Gamma Setting for GS15 |  |

| D/C#   | Hex          | <b>D</b> 7 | D6                  | D5      | D4      | D3                  | D2                  | D2                  | D0                  | Command                                      | Description                                                                                                                                                                                                                                                                                                       |  |  |

|--------|--------------|------------|---------------------|---------|---------|---------------------|---------------------|---------------------|---------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        |              |            |                     |         |         |                     |                     |                     |                     |                                              | Note<br><sup>(1)</sup> 0 ≤ Setting of GS1 < Setting of GS2 < Setting of GS3<br>< Setting of GS14 < Setting of GS15<br>Refer to Section 8.8 for details<br><sup>(2)</sup> The setting must be followed by the Enable Gray Scale<br>Table command (00h)                                                             |  |  |

| 0      | B9           | 1          | 0                   | 1       | 1       | 1                   | 0                   | 0                   | 1                   | Select Default<br>Linear Gray<br>Scale table | The default Linear Gray Scale table is set in unit of DCLK's<br>as follow<br>GS0 level pulse width = 0;<br>GS1 level pulse width = 0;<br>GS2 level pulse width = 8;<br>GS3 level pulse width = 16;<br>:<br>:<br>GS14 level pulse width = 104;<br>GS15 level pulse width = 112<br>Refer to Section 8.8 for details |  |  |

| 0      | BB<br>A[4:0] | 1 *        | 0*                  | 1 *     | 1<br>A, | 1<br>A <sub>3</sub> | 0<br>A <sub>2</sub> | 1<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | Set Pre-charge<br>voltage                    | A[5:1]         Hex code         pre-charge voltage           00000         00h         0.20 x V <sub>CC</sub> :         :         :           11111         3Eh         0.60 x V <sub>CC</sub>                                                                                                                    |  |  |

| 0      | BE<br>A[3:0] | 1 *        | 0*                  | 1 *     | 1 *     | 1<br>A3             | 1<br>A2             | 1<br>A <sub>1</sub> | 0<br>A <sub>0</sub> | Set V <sub>oomt</sub>                        | Set COM deselect voltage level [reset = 04h]<br>A[3:0] =<br>A[2:0] Hex code V <sub>COMH</sub><br>0000 00h 0.72 x V <sub>CC</sub><br>: : : :<br>0100 04h 0.80 x V <sub>CC</sub><br>: : : :<br>0111 07h 0.86 x V <sub>CC</sub>                                                                                      |  |  |

| 0<br>1 | C1<br>A[7:0] | 1<br>A,    | 1<br>A <sub>6</sub> | 0<br>A5 | 0<br>A4 | 0<br>A3             | 0<br>A <sub>2</sub> | 0<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | Set Contrast<br>Current                      | A[7:0]: Contrast current value, range:00h~FFh,<br>i.e. 256 steps for I <sub>SEO</sub> current [reset = 7Fh]                                                                                                                                                                                                       |  |  |

| 0      | C7<br>A[3:0] | 1 *        | 1 *                 | 0*      | 0*      | 0<br>A3             | 1<br>A <sub>2</sub> | 1<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | Master Contrast<br>Current Control           | 1 · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                           |  |  |

| 0      | CA<br>A[6:0] | 1          | 1<br>A6             | 0<br>As | 0<br>A4 | 1<br>A3             | 0<br>A2             | 1<br>A1             | 0<br>A <sub>0</sub> | Set MUX Ratio                                | A[6:0]: Set MUX ratio from 16MUX ~ 128MUX<br>A[6:0] = 15d represents 16MUX<br>:<br>A[6:0] = 127d represents 128MUX [reset]                                                                                                                                                                                        |  |  |

| D/C#        | Hex                | <b>D</b> 7  | D6          | D5           | D4           | D3          | D2      | D2          | <b>D</b> 0  | Command             | Description                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------|-------------|-------------|--------------|--------------|-------------|---------|-------------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>1 | D1<br>A[5:4]<br>20 | 1<br>1<br>0 | 1<br>0<br>0 | 0<br>A5<br>1 | 1<br>A4<br>0 | 0<br>0<br>0 | 000     | 0<br>1<br>0 | 1<br>0<br>0 |                     | A[5:4] = 00b: Reserved<br>A[5:4] = 10b: Normal [reset]                                                                                                                                                                                                                                                                                     |

| 0           | FD<br>A[2]         | 1 0         | 1 0         | 1 0          | 1            | 1 0         | 1<br>A2 | 0           | 1 0         | Set Command<br>Lock | A[2]: MCU protection status [reset = 12h]<br>A[2] = 0b, Unlock OLED driver IC MCU interface from<br>entering command [reset]<br>A[2] = 1b, Lock OLED driver IC MCU interface from<br>entering command<br>Note<br><sup>(1)</sup> The locked OLED driver IC MCU interface prohibits all<br>commands and memory access except the FDh command |

Note (1) \*\* stands for "Don't care".

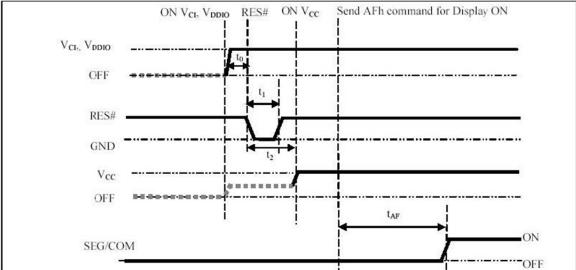

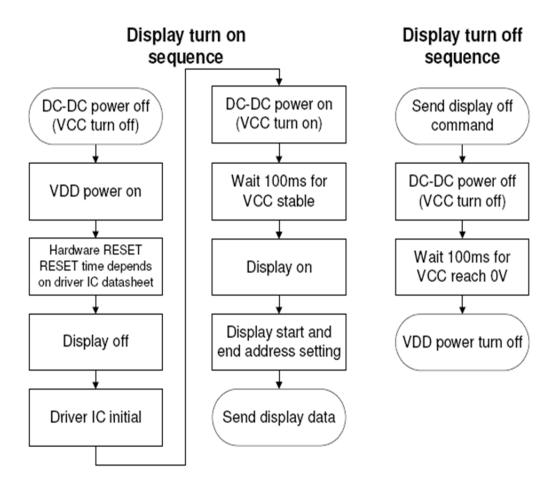

## 9.3 Power ON / OFF Sequence & Application Circuit

#### **POWER ON / OFF SEQUENCE**

#### **Power ON sequence:**

- 1. Power ON VDD

- 2. After VDD become stable, set wait time at least 1ms (t0) for internal VDD become stable. Then set RES# pin LOW (logic low) for at least 100us (t1) (4) and then HIGH (logic high).

- 3. After set RES# pin LOW (logic low), wait for at least 100us (t2). Then Power ON VCC.(1)

- 4. After VCC become stable, send command AFh for display ON. SEG/COM will be ON after 200ms (tAF).

#### **Power OFF sequence**:

- 1. Send command AEh for display OFF.

- 2. Power OFF VCC.(1), (2)

- 3.Wait for tOFF. Power OFF VCI, VDDIO. (where Minimum tOFF=80ms (3), Typical tOFF=100ms)

#### Note:

- (1) Since an ESD protection circuit is connected between VCI, VDDIO and VCC, VCC becomes lower than VCI whenever VCI, VDDIO is ON and VCC is OFF as shown in the dotted line of VCC.

- (2) VCC should be kept float (disable) when it is OFF.

- (3) VCI, VDDIO should not be Power OFF before VCC Power OFF.

- (4) The register values are reset after t1.

- (5) Power pins (VCI, VCC) can never be pulled to ground under any circumstance.

# 10 Quality Assurance

## **10.1 Inspection conditions**

- 1. The inspection and meaurement are performed under the following conditions,

- 2. unless otherwise specified.

- 3. Temperature: 25±5°C

- 4. Humidity: 50±10%R.H.

- 5. Distance between the panel and eyes of the inspector  $\geq\!30\text{cm}$

## **10.2 Inspection Parameters**

| Severity | Inspection Item | Defect                          | Remark     |  |  |

|----------|-----------------|---------------------------------|------------|--|--|

|          |                 | (1) Non-displaying              |            |  |  |

|          | 1. Panel        | (2) Line defects                |            |  |  |

|          |                 | (3) Malfunction                 |            |  |  |

| Major    |                 | (4) Glass cracked               |            |  |  |

| Defect   | 2. Film         | (1) Film dimension out of       | Can not be |  |  |

|          | Z. I IIIII      | specification                   | assembled  |  |  |

|          | 3. Dimension    | (1) Outline dimension out       |            |  |  |

|          | 0. Difficition  | of specification                |            |  |  |

|          |                 | (1) Glass scratch               |            |  |  |

|          | 1. Panel        | (2) Glass cutting NG            |            |  |  |

|          |                 | (3) Glass chip                  |            |  |  |

|          |                 | (1) Polarizer scratch           | Appearance |  |  |

| Minor    | 2. Polarizer    | Polarizer (2) Stains on surface |            |  |  |

| Defect   |                 | (3) Polarizer bubbles           | defect     |  |  |

|          |                 | (1) Dim spot 、                  | ueleci     |  |  |

|          | 3. Displaying   | Bright spot 🗸 dust              |            |  |  |

|          | 4. Film         | (1) Damage                      | ]          |  |  |

|          | 4. [111]        | (2) Foreign material            |            |  |  |

| Description       |                                      | Criterion            |                        |             | AQL   |

|-------------------|--------------------------------------|----------------------|------------------------|-------------|-------|

|                   | Width (mm)<br>W                      | Length (mm)<br>L     | numbe<br>piec<br>permi | es<br>itted |       |

| 1. Glass scratch  | W≦0.03<br>0.03< W≦0.05               | lgnore<br>L≦3        | lgno<br>3              |             | Minor |

|                   | 0.05< W                              |                      | Nor                    | ne          |       |

|                   | beyond A.A.                          |                      | Igno                   | ore         |       |

|                   |                                      |                      |                        |             |       |

|                   | Size                                 | number<br>pieces per | mitted                 |             |       |

| 2. Polarizer      | Φ≦0.2                                | Ignor                | e                      |             |       |

| bubble            | $0.2 < \Phi \le 0.5$<br>$0.5 < \Phi$ | 2                    |                        |             | Minor |

|                   | beyond A.A.                          | Ignor                | e                      |             |       |

|                   |                                      |                      | -                      | 1           |       |

|                   | average                              | numbe                | rof                    |             |       |

|                   |                                      |                      |                        |             |       |

|                   | D ≦0.1                               | Ignor                | е                      |             |       |

| 3. Dimming spot 🕥 | 0.1 < D ≦0.15                        |                      |                        |             |       |

| Lighting spot     | 0.15< D ≦0.2                         |                      |                        |             | Minor |

| Dust              | 0.2 < D                              |                      |                        |             |       |

|                   | beyond A.A.<br>D=(long diamete       | Ignor                |                        |             |       |

|                   | Pixel off is not allo                |                      |                        |             |       |

|                   |                                      |                      |                        |             |       |

### **10.3 WARRANTY POLICY**

We will provide one-year warranty for the products only if under specification operating conditions.

If there are functional defects found during the period of warranty, the defective products would be replaced on a one-to-one basis.

We would not be responsible for any direct/indirect liabilities consequential to any parties.

#### 10.4 MTBF

10.4.1 .MTBF based on specific test condition is 26K hours.

10.4.2 Test Condition:

10.4.2.1 Supply Voltage: Vcc=14.5V

10.4.2.2 Luminance: 90cd/m2

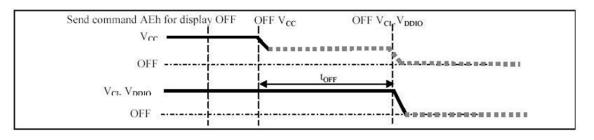

- 10.4.2.3 Operation temperature and humidity: 25  $\,^\circ\!C\,$  and 50%RH

- 10.4.2.4 Run-Patterns:

10.4.3 Test Criteria:

Luminace has decayed to less than 50% of the initial measured luminance.

# 11.Reliability

#### ■Content of Reliability Test

| NO. | Items.                                     | Specification                                                                                             | Applicable<br>Standard |  |  |  |

|-----|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|--|--|--|

| 1   | High temp. (Non-operation)                 | 85°C, 240hrs                                                                                              |                        |  |  |  |

| 2   | High temp. (Operation)                     | 70°C, 120hrs                                                                                              |                        |  |  |  |

| 3   | Low temp. (Operation)                      | -40°C, 120hrs                                                                                             |                        |  |  |  |

| 4   | High temp. / High. humidity<br>(Operation) | 65°C, 90%RH, 120hrs                                                                                       |                        |  |  |  |

| 5   | Thermal<br>shock(Non-operation)            | -40°C ~85°C (-40°C /30min;<br>transit /3min; 85°C /30min;<br>transit /3min) 1cycle: 66min,<br>100 cycles. |                        |  |  |  |

| 6   | Vibration                                  | Frequency : 5~50HZ, 0.5G<br>Scan rate : 1 oct/min<br>Time : 2 hrs/axis<br>Test axis : X, Y, Z             |                        |  |  |  |

#### Test and measurement conditions

- 1. All measurements shall not be started until the specimens attain to temperature stability.

- 2. All-pixels-on is used as operation test pattern.

- 3. The degradation of Polarizer are ignored for item 1 & 4 & 5.

#### Criteria

- 1. The function test is OK.

- 2. No observable defects.

- 3. Luminance: >50% of initial value.

- 4. Current consumption : within ±50% of initial value.

#### **Reliability Test**

We only guarantees the reliability of the panel under the test conditions and durations listed in the specification, and is not responsible for any test results that are conducted using more stringent conditions and/or with lengthened durations. Also, when the testing the panel in a chamber or oven, make sure they won't produce any condensation on the panel, especially on the electrical leads, before lighting on the panel to see if it passes the test. Also the panel should rest for about an hour at room temperature and pressure before the measurement, as indicated in the specification. Be aware that one should use fresh panel for each of the reliability test items listed in the specification, in other words, don't use the panels that were tested for subsequent tests.

### 12.Precautions for Handling

- 12.1 When handling the module, wear powder-free antistatic rubber finger cots, and be careful not to bend and twist it.

- 12.2 The OLED module is consisted of glass and film, and it should avoid pressure, strong impact, or being dropped from a height.

- 12.3 The OLED module is an electronic component and is subject to damage caused by Electro Static

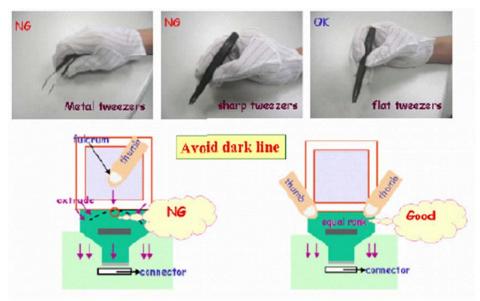

Discharge (ESD) and hence normal ESD precautions must be taken when handling it. Also, appropriate ESD protective environment must be administered and maintained in the production line. When handling and assembling the panel, wear an antistatic wrist strap with the alligator clip attached to the ground to prevent ESD damage on the panel. Also, ground the tools being used for panel assembly and make sure the working environment is not too dry to cause ESD problems. (See the photos below).

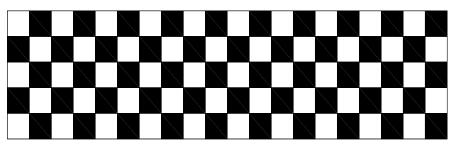

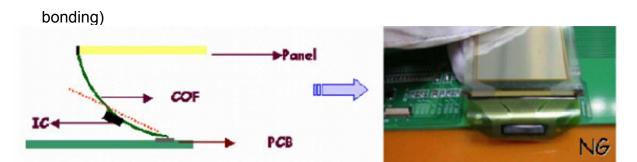

12.4 Please do not bend the film near the substrate glass.(this could cause film peeling and COF damage) and the peeling strength about 600g/cm, the bending <20times and the bending radius :R>0.8mm

12.5 Avoid bending the film at IC bonding area.(>1.5mm)(this could damage the ILB

12.6 Use both thumbs to insert COF into the connector when assembling the panel. See the photo on the far right below for correct insertion of the film into the connector (one-handed insertion exerts uneven force on the film and could cause its breakage, photo on the left)

12.7 Do not wipe the pin of film with the dry or hard materials that will damage the surface. When cleaning the display surface, use soft cloth solvent and wipe gently (Recommend solvent: IPA, alcohol), and do not wipe the display with dry or hard materials that will damage the polarizer surface and do not use the solvent like: Water, Acetone, Aromatic

## 13. Precautions for Electrical

#### 13.1. Design using the settings in the specification

It is extremely important to design and operate the panel using the settings listed in the specification. This includes voltage, current, frame rate, duty cycle... etc. Operation of the OLED outside the specified range in the specification should be entirely avoided to ensure proper operation of the OLED.

#### 13.2. Maximum Ratings

To ensure proper operation of the panel, never design the panel with parameters running over the maximum ratings listed in the specification. Also the logic voltages such as VIL and VIH have to be within the specified range in the specification to prevent any improper operation of the panel.

#### 13.3 Power on/off procedure

Any operation that does not comply with the procedure could cause permanent damage of the IC and should be avoided. When the logic power is not on, do not activate any input signal. Abrupt shutdown of power to the module, while the OLED panel is on, could cause OLED panel malfunctioning.

#### 13.4 Power savings

To save power consumption of the OLED, one can use partial display or sleep mode when the panel is not fully activated. Also, if possible, make maximum use of black background to save power. The OLED is a self-luminous device, and a particular pixel cluster or image can be lit on via software control, so power savings can be achieved by partial display or dimming down the luminance. Depending on the application, the user can choose among Ultra Bright Mode, Normal Operation Mode, and Sleeping Mode.

The power consumption is almost in direct proportion to the brightness of the panel, and also in direct proportion to the number of pixels lit on the panel, so the customer can save the power by the use of black background and Sleeping Mode. One benefit from using these design schemes is the extension of the OLED lifetime.

#### 13.5 Residual Image (Image Sticking)

The OLED is a self-emissive device. As with other self-emissive device or displays consisting of self-emissive pixels, when a static image frozen for a long period of time is changed to another one with all-pixels-on background, residual image or image sticking is noticed by the human eye. Image sticking is due to the luminance difference or contrast between the pixels that were previously turned on and the pixels that are newly turned on. The time when image sticking happens depends on the luminance decay curve of the display. The slower the decay, the less prominent the image sticking is. It is strongly recommended that the user employ the following three strategies to minimize image sticking

- 13.5.1Employ image scrolling or animation to even out the lit-on time of each and every pixel on the display, also could use sleeping mode for reduced the residual image and extend the power capacity.

- 13.5.2Minimize the use of all-pixels-on or full white background in their application because when the panel is turned on full white, the image sticking from previously shown patterns is the most revealing. Black background is the best for power savings, greatest visibility, eye appealing, and dazzling displays

- 13.5.3If in the reliability test when a static logo is used, change the pattern into its inverse (i.e., turn off the while pixels and turn on the previously unlit pixels) and freeze the inverse pattern as long as the original logo is used, so every pixel on the panel can be lit on for about the same time to minimize image sticking, caused by the differential turn-on time between the original and its reverse patterns

#### 14. Precautions for Storage

Although the storage conditions and guarantee period are indicated in the specification, it is advisable to store the packed cartons or packages at  $23^{\circ}C\pm5^{\circ}C$ ,55%±10%RH, Do not store the OLED module under direct sunlight or UV light and for best panel performance, unpack the cartons and start the production with the panels within one months after the reception of them.