# **TFT Module Specification**

## MODEL: 13-080ZIMA0GA0-S

- <  $\diamondsuit$  > PRELIMINARY SPECIFICATION

- < ◆ > APPROVAL SPECIFICATION

| CUSTOMER    |

|-------------|

|             |

|             |

|             |

| APPROVED BY |

|             |

|             |

|             |

| DATE:       |

| DESIGNED   | CHECKED    | APPROVED   |

|------------|------------|------------|

| RD         | PM         | 批准         |

| 2020.12.23 | 2020.12.23 | 2020.12.23 |

| 趙長慶        | 呂家祥        | PM         |

DigiWise International Corporation

3F., No.10, Ln 83, Sec 1, Guang Fu Rd., Sanchong Dist., 24158,

New Taipei City, Taiwan (ROC)

TEL: +886-2-29992866 FAX: +886-2-29990900

## **RECORD OF REVISION**

| Version | Revised Date | Page | Content                   |

|---------|--------------|------|---------------------------|

| V1.0    | 2020/12/23   |      | PRELIMINARY SPECIFICATION |

|         |              |      |                           |

|         |              |      |                           |

|         |              |      |                           |

|         |              |      |                           |

## **TABLE OF CONTENTS**

| No. | Content                              | Page |

|-----|--------------------------------------|------|

| TFT | Module Specification                 | 1    |

|     | E OF CONTENTS                        |      |

| 1.  | GENERAL DESCRIPTION                  | 4    |

| 2.  | MECHANICAL SPECIFICATION             | 5    |

| 3.  | PIN DESCRIPTION                      | 6    |

| 4.  | ABSOLUTE MAXIMUM RATINGS             | 8    |

| 5.  | BLOCK DIAGRAM                        | 9    |

| 6.  | ELECTRICAL CHARACTERISTICS           | 10   |

| 7.  | AC CHARACTERISTICS                   | 15   |

| 8.  | OPTICAL CHARACTERISTICS              | 23   |

| 9.  | RELIABILITY                          | 26   |

| 10. | PRECAUTION RELATING PRODUCT HANDLING | 31   |

#### 1. GENERAL DESCRIPTION

### 1.1 Description

The specification is model 13-080ZIMA0GA0-S is a color active matrix thin film transistor (TFT) liquid crystal display (LCD) that uses amorphous silicon TFT as a switching device. This model is composed of a TFT LCD panel, a driving circuit, a backlight system. This TFT LCD has a 8 inch diagonally measured active display area with HD (800 horizontal by 1280 vertical pixels) resolution.

#### 1.2 Features:

| No. | Item                                                            | Specification                       | Unit   |

|-----|-----------------------------------------------------------------|-------------------------------------|--------|

| 1   | Panel Size                                                      | 8"                                  | Inch   |

| 2   | Number of Pixels                                                | 800 (W) x RGB x 1280 (H)            | Pixels |

| 3   | Active Area                                                     | 107.64 (W) × 172.22 (H)             | mm     |

| 4   | Pixel Pitch                                                     | 0.13455 (W) x 0.13455 (H)           | mm     |

| 5   | Outline Dimension 114.6 (W) $\times$ 184.1 (H) $\times$ 2.6 (7) |                                     | mm     |

| 6   | Number of Colors                                                | 16.7M                               |        |

| 7   | Display Mode                                                    | IPS / Normally Black / Transmissive |        |

| 8   | View Direction                                                  | Free direction                      |        |

| 9   | Display Format                                                  | RGB vertical stripe                 |        |

| 10  | Surface Treatment                                               | Anti-Glare                          |        |

| 11  | Contrast Ratio                                                  | 800 (Typ.)                          |        |

| 12  | Luminance (cd/m^2)                                              | 450 (Typ.)                          | cd/m2  |

| 13  | Interface                                                       | MIPI DSI 4 lane                     |        |

| 14  | Backlight                                                       | White LED                           |        |

| 15  | Driver IC                                                       | IL19881C                            |        |

| 16  | Operation Temperature                                           | -10 ~ 60                            | °C     |

| 17  | Storage Temperature                                             | -20 ~ 70                            | °C     |

| 18  | Weight                                                          | (110)                               | g      |

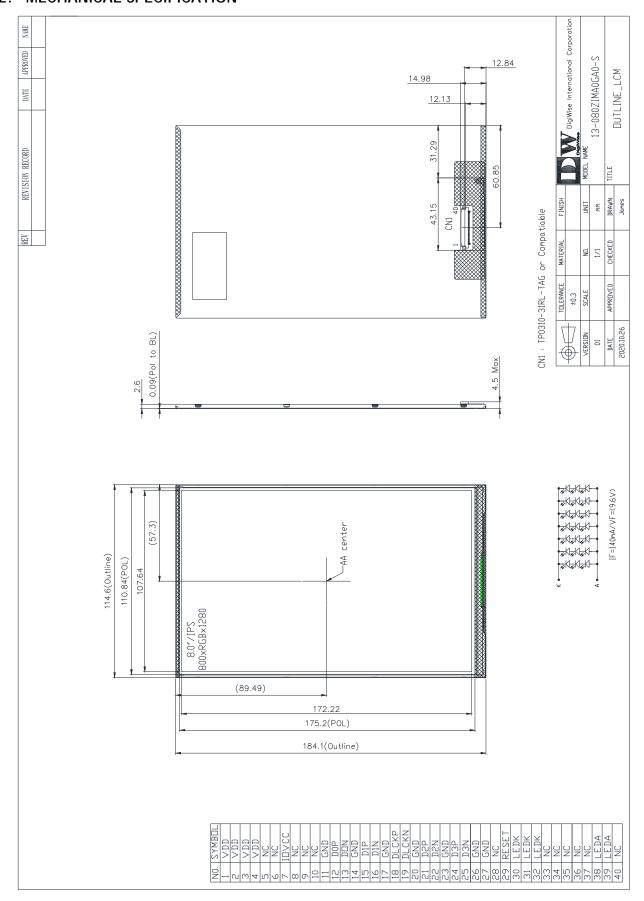

## 2. MECHANICAL SPECIFICATION

#### 3. PIN DESCRIPTION

| Pin No. | Symbol | 1/0 | Function                               | Note |

|---------|--------|-----|----------------------------------------|------|

| 1       | VDD    | Р   | Power Supply voltage +3.3V             | (1)  |

| 2       | VDD    | Р   | Power Supply voltage +3.3V             |      |

| 3       | VDD    | Р   | Power Supply voltage +3.3V             |      |

| 4       | VDD    | Р   | Power Supply voltage +3.3V             |      |

| 5       | NC     | -   | No connection                          |      |

| 6       | NC     | -   | No connection                          |      |

| 7       | IOVCC  | Р   | Power Supply Logic voltage +1.8V       |      |

| 8       | NC     | -   | No connection                          |      |

| 9       | NC     | -   | No connection                          |      |

| 10      | NC     | -   | No connection                          |      |

| 11      | GND    | Р   | Ground                                 |      |

| 12      | D0P    | I   | Positive MIPI differential data input  |      |

| 13      | DON    | I   | Negative MIPI differential data input  |      |

| 14      | GND    | Р   | Ground                                 |      |

| 15      | D1P    | I   | Positive MIPI differential data input  |      |

| 16      | D1N    | I   | Negative MIPI differential data input  |      |

| 17      | GND    | Р   | Ground                                 |      |

| 18      | DCLKP  | I   | Positive MIPI differential clock input |      |

| 19      | DCLKN  | I   | Negative MIPI differential clock input |      |

| 20      | GND    | Р   | Ground                                 |      |

| 21      | D2P    | I   | Positive MIPI differential data input  |      |

| 22      | D2N    | I   | Negative MIPI differential data input  |      |

| 23      | GND    | Р   | Ground                                 |      |

| 24      | D3P    |     | Positive MIPI differential data input  |      |

| 25      | D3N    | I   | Negative MIPI differential data input  |      |

| 26      | GND    | Р   | Ground                                 |      |

| 27      | GND    | Р   | Ground                                 |      |

| 28      | NC     | -   | No connection                          |      |

| 29      | RST    |     | Global reset pin                       |      |

| 30      | LEDK   | Р   | LED Cathode                            |      |

| 31      | LEDK   | Р   | LED Cathode                            |      |

| 32      | LEDK   | Р   | LED Cathode                            |      |

| 33      | NC     | -   | No connection                          |      |

| 34      | NC     | -   | No connection                          |      |

| 35      | NC     | -   | No connection                          |      |

| 36      | NC     |     | No connection                          |      |

| 37      | NC     | -   | No connection                          |      |

| 38      | LEDA   | Р   | LED Anode                              |      |

| 39      | LEDA   | Р   | LED Anode                              |      |

#### 4. ABSOLUTE MAXIMUM RATINGS

## 4.1 Electrical Absolute Rating

## 4.1.1 TFT LCD Module

| ltom                 | Cumbal | Val  | ues  | Unit  | Note |

|----------------------|--------|------|------|-------|------|

| Item                 | Symbol | Min. | Max. | Ullit |      |

| Dower cumply yeltogo | VDD    | -0.3 | +3.8 | V     |      |

| Power supply voltage | IOVCC  | -0.3 | +3.8 | V     |      |

## 4.1.2 Environment Absolute Rating

| ltom                  | Itom Symbol |      | Values | Unit | Noto |             |  |

|-----------------------|-------------|------|--------|------|------|-------------|--|

| Item                  | Symbol      | Min. | Тур.   | Max. | Unit | Note        |  |

| Operating Temperature | Тора        | -10  |        | 60   | °C   | Ambient     |  |

| Storage Temperature   | Tstg        | -20  |        | 70   | °C   | temperature |  |

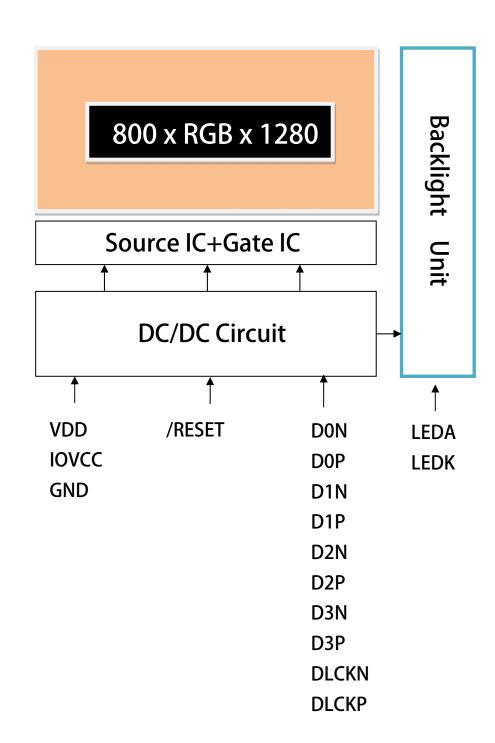

#### 5. BLOCK DIAGRAM

#### 5.1 TFT LCD Module

#### 6. ELECTRICAL CHARACTERISTICS

#### 6.1 DC Characteristics for Panel Driving

| Item              |                      | Symbol |           | Unit | Note      |       |      |

|-------------------|----------------------|--------|-----------|------|-----------|-------|------|

| Item              |                      | Symbol | Min.      | Тур. | Max.      | Ullit | Note |

| Dower cumply      | voltago              | VDD    | 2.6       | 3.3  | 3.6       | ٧     |      |

| Power suppry      | Power supply voltage |        | 1.65      | 1.8  | 3.6       | V     |      |

| Input             |                      |        | 0.7xIOVCC | -    | IOVCC     | V     |      |

| Voltage for logic | L Level              | VIL    | -0.3      | -    | 0.3xIOVCC | V     |      |

| Digital Curren    | t                    | IDD    | -         | TBD  | -         | mA    |      |

#### 6.2 DSI DC Characteristics

The DSI uses different state codes which depend on DC voltage levels of the clock and data lanes. The meaning of the state codes is defined in the following table

| Ctata Cada | Line DC Voltage Levels |                   |  |  |  |

|------------|------------------------|-------------------|--|--|--|

| State Code | CLOCK_P or DATA_P      | CLOCK_N or DATA_N |  |  |  |

| HS-0       | Low (HS)               | High (HS)         |  |  |  |

| HS-1       | High (HS)              | Low (HS)          |  |  |  |

| LP-00      | Low (LP)               | Low (LP)          |  |  |  |

| LP-01      | Low (LP)               | High (LP)         |  |  |  |

| LP-10      | High (LP)              | Low (LP)          |  |  |  |

| LP-11      | High (LP)              | High (LP)         |  |  |  |

#### 6.2.1 DC Characteristics for DSI LP Mode

DC levels of the LP-00, LP-01, LP-10 and LP-11 are defined in the table below: DC Characteristics for the DSI LP mode when LP-RX, LP-CD or LP-TX is mentioned in the condition column. Other logical levels in the table are for MCU interface.

| Davamatan              | O. mahal            | Condition                   |      | Specification |      | Unit |

|------------------------|---------------------|-----------------------------|------|---------------|------|------|

| Parameter              | Symbol              | Condition                   | Min. | Тур.          | Max. |      |

| Logic 1 input voltage  | V <sub>IHLPCD</sub> | LP-CD                       | 450  | -             | 1350 | m∨   |

| Logic 0 input voltage  | VILLPCD             | LP-CD                       | 0.0  | -             | 200  | m∨   |

| Logic 1 input voltage  | VIHLPRX             | LP-RX (CLK, D0 ,D1, D2, D3) | 880  | -             | 1350 | m∨   |

| Logic 0 input voltage  | $V_{ILLPRX}$        | LP-RX (CLK, D0 ,D1, D2, D3) | 0.0  | -             | 550  | m∨   |

| Logic 0 input voltage  | VILLPRXULP          | LP-RX (CLK ULP mode)        | 0.0  | -             | 300  | m∨   |

| Logic 1 output voltage | V <sub>OHLPTX</sub> | LP-TX (D0)                  | 1.1  | -             | 1.3  | V    |

| Logic 0 output voltage | V <sub>OLLPTX</sub> | LP-TX (D0)                  | -50  | -             | 50   | m∨   |

| Logic 1 input current  | I <sub>IH</sub>     | LP-CD, LP-RX                | -    | -             | 10   | uA   |

| Logic 0 input current  | I <sub>IL</sub>     | LP-CD, LP-RX                | -10  | -             | -    | uA   |

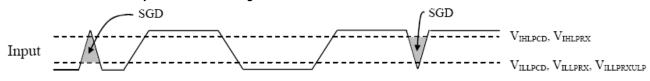

### 6.2.2 Spike/Glitch Rejection

#### Notes:

- 1. A spike/glitch can be rejected when the Peak Interference Amplitude is 200mV (at maximum) and Interference Frequency is 450MHz (at the very least).

- 2. n = 0 and 1.

| Spike/Glitch Rejection – DSI |        |                               |     |     |      |  |

|------------------------------|--------|-------------------------------|-----|-----|------|--|

| Signal                       | Symbol | Parameter                     | Min | Max | Unit |  |

| CLKP/N, DnP/N                | SGD    | Input pulse rejection for DSI | -   | 300 | ∨ps  |  |

#### 6.2.3 DC Characteristics for DSI HS mode

| Parameter                                                         | Symbol                  | Condition                                        | Specification |     |     | Unit |

|-------------------------------------------------------------------|-------------------------|--------------------------------------------------|---------------|-----|-----|------|

| Input Common Mode ∀oltage for Clock                               | Vcmclk                  | CLKP/N<br>Note 2, Note 3                         | 70            | -   | 330 | m∨   |

| Input Common Mode ∀oltage for Data                                | Vcmdata                 | DnP/N V <sub>CMDATA</sub> Note 2, Note 3, Note 5 |               | -   | 330 | m∨   |

| Common Mode Ripple for Clock Equal or Less<br>than 450MHz         | V <sub>CMRCLKL450</sub> | CLKP/N<br>Note 4                                 | -50           | -   | 50  | m∨   |

| Common Mode Ripple for Data Equal or Less<br>than 450MHz          | VcMRDATAL450            | DnP/N<br>Note 4, Note 5                          | -50           | -   | 50  | m∨   |

| Common Mode Ripple for Clock More than<br>450MHz (peak sine wave) | Vcmrclkm450             | CLKP/N                                           | -             | -   | 100 | m∨   |

| Common Mode Ripple for Data More than<br>450MHz (peak sine wave)  | VCMRDATAM450            | DnP/N<br>Note 5                                  | -             | -   | 100 | m∨   |

| Differential Input Low Level Threshold ∀oltage for Clock          | V <sub>THLCLK</sub> -   | CLKP/N                                           | -70           | -   | -   | m∨   |

| Differential Input Low Level Threshold ∀oltage for Data           | V <sub>THLDATA</sub> -  | DnP/N<br>Note 5                                  | -70           | -   | -   | m∨   |

| Differential Input High Level Threshold ∀oltage for Clock         | V <sub>THHCLK+</sub>    | CLKP/N                                           | -             | -   | 70  | m∨   |

| Differential Input High Level Threshold ∀oltage<br>for Data       | V <sub>THHDATA</sub> +  | DnP/N<br>Note 5                                  | -             | -   | 70  | m∨   |

| Single-ended Input Low Voltage                                    | VILHS                   | CLKP/N, DnP/N<br>Note 3, Note 5                  | -40           | -   | -   | m∨   |

| Single-ended Input High ∀oltage                                   | V <sub>IHHS</sub>       | CLKP/N, DnP/N<br>Note 3, Note 5                  | -             | -   | 460 | m∨   |

| Differential Termination Resistor                                 | R <sub>TERM</sub>       | CLKP/N, DnP/N<br>Note 5                          | 80            | 100 | 125 | Ω    |

| Single-ended Threshold Voltage for<br>Termination Enable          | V <sub>TERM-EN</sub>    | CLKP/N, DnP/N<br>Note 5                          | -             | -   | 450 | m∨   |

| Termination Capacitor                                             | C <sub>TERM</sub>       | CLKP/N, DnP/N<br>Note 5, Note 6                  | -             | -   | 60  | pF   |

#### Notes:

1. Ta = -30 $^{\circ}$ C to 70 $^{\circ}$ C (to +85 $^{\circ}$ C no damage) , VDD = 2.5V to 6.6V, IOVCC = 1.65V to 3.6V

DigiWise

E-mail: sales@digiwise.asia

- 2. Includes 50mV (-50mV to 50mV) ground difference

- 3. Without VCMRCLKM450/VCMRDATAM450

- 4. Without 50mV (-50mV to 50mV) ground difference

- 5. n = 0 and 1

- 6. For higher bit rates, a 14pF capacitor will be needed to meet the common-mode return loss specification.

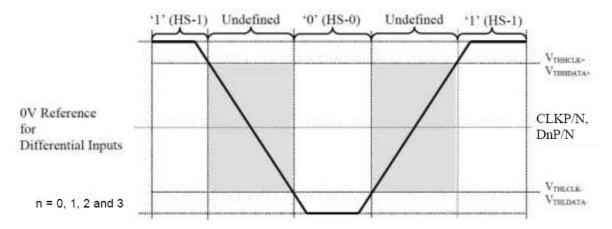

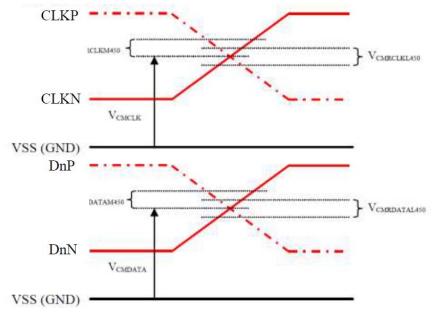

The DSI receiver (HS mode) understands that there is logical 1 (= HS-1) when a differential voltage is more than VTHH (CLKP/DnP). The DSI receiver (HS mode) understands that there is logical 0 (= HS-0) when a differential voltage is more than VTHL (CLKN/DnN). There is undefined state if the differential voltage is less than VTHH (CLKP/DnP) and less than VTHL (CLKN/DnN). A reference figure is below.

Differential Inputs Logical 0 and 1, Threshold High/Low, Differential Voltage Range

**Common Mode Voltage on Clock and Data Channels**

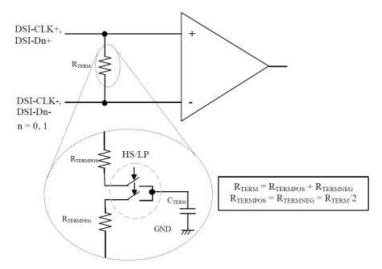

The termination resistor (RTERM) of the differential DSI receiver can be driven to two different states by the receiver:

%High Speed (HS) mode when the termination resistor is connected between differential inputs (CLKP<=> CLKN or D0P <=> D0N or D1P <=> D2N or D2P <=> D3N)

The termination switch (HS/LP), when the termination resistor is not connected, is illustrated below.

Differential Pair Termination Resistor on the Receiver Side

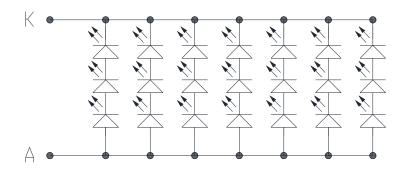

## 6.3 Backlight Unit

| ltem                 | Symbol | Value |       |      | Unit  | Condition |  |

|----------------------|--------|-------|-------|------|-------|-----------|--|

| item                 | Symbol | Min.  | Тур.  | Max. | Ullit | Condition |  |

| LED Voltage          | VL     | 1     | (9.6) | 1    | V     |           |  |

| LED Current          | IL     | -     | 140   | -    | mA    | 3S7P      |  |

| Power Consumption    | PBL    | -     | 1.344 | -    | W     |           |  |

| LED Life Time (25°€) | -      | 50000 | -     | -    | hr    | (1)       |  |

Note (1): The "LED life time" is defined as the module brightness decrease to 50% original brightness that the ambient temperature is  $25^{\circ}$ C 60% RH.

#### 7. AC CHARACTERISTICS

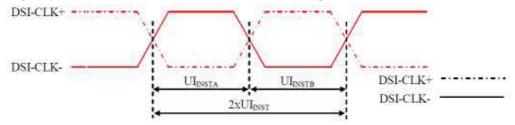

#### 7.1 High Speed Mode - Clock Channel Timing

| Signal | Symbol                                               | Parameter               | Min    | Max  | Unit |

|--------|------------------------------------------------------|-------------------------|--------|------|------|

| CLKP/N | 2xUI <sub>INST</sub>                                 | Double UI instantaneous | Note 2 | 25   | ns   |

| CLKP/N | UI <sub>INSTA</sub> ,UI <sub>INSTB</sub><br>(Note 1) | UI instantaneous Half   | Note 2 | 12.5 | ns   |

#### Notes:

- 1. UI = UIINSTA = UIINSTB

- 2. Define the minimum value, see below.

| Data type                                                   | Two Lanes<br>speed | Three Lanes speed | Four Lanes<br>speed |

|-------------------------------------------------------------|--------------------|-------------------|---------------------|

| Data Type = 00 1110 (0Eh), RGB 565, 16 UI per Pixel         | 566 Mbps           | 466 Mbps          | 366 Mbps            |

| Data Type = 01 1110 (1Eh), RGB 666, 18 UI per Pixel         | 637 Mbps           | 525 Mbps          | 412 Mbps            |

| Data Type = 10 1110 (2Eh), RGB 666 Loosely, 24 UI per Pixel | 850 Mbps           | 700 Mbps          | 550 Mbps            |

| Data Type = 11 1110 (3Eh), RGB 888, 24 UI per Pixel         | 850 Mbps           | 700 Mbps          | 550 Mbps            |

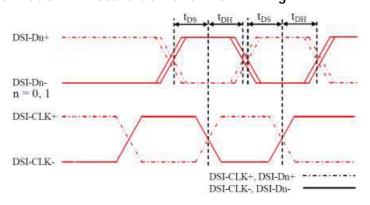

## 7.2 High Speed Mode - Data Clock Channel Timing

| Signal Symbol     |                 | Parameter                | Min     | Max |

|-------------------|-----------------|--------------------------|---------|-----|

|                   | t <sub>DS</sub> | Data to Clock Setup time | 0.15xUI | -   |

| DnP/N , n=0 and 1 | t <sub>DH</sub> | Clock to Data Hold Time  | 0.15xUI | -   |

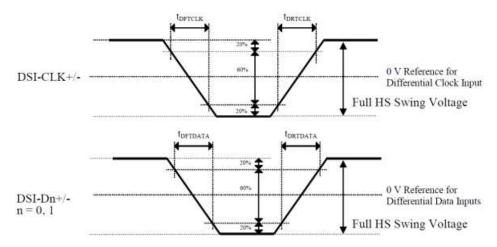

### 7.3 High Speed Mode - Rising and Falling Timings

| Barranatan                        | Ob. a.l              | 0         | Specification |     |        |

|-----------------------------------|----------------------|-----------|---------------|-----|--------|

| Parameter                         | Symbol               | Condition | Min           | Тур | Max    |

| Differential Disc Times for Clask |                      | CLKD/N    | 150           |     | 0.3UI  |

| Differential Rise Time for Clock  | t <sub>DRTCLK</sub>  | CLKP/N    | 150 ps        | -   | (Note) |

| Differential Bios Times for Date  |                      | DnP/N     | 150           |     | 0.3UI  |

| Differential Rise Time for Data   | <b>t</b> DRTDATA     | n=0 and 1 | 150 ps        | •   | (Note) |

| Differential Fall Time for Clask  |                      | CLKD/N    | 150           |     | 0.3UI  |

| Differential Fall Time for Clock  | tDFTCLK              | CLKP/N    | 150 ps        | -   | (Note) |

| Differential Call Times for Date  |                      | DnP/N     | 150           |     | 0.3UI  |

| Differential Fall Time for Data   | t <sub>DFTDATA</sub> | n=0 and 1 | 150 ps        | -   | (Note) |

Note: The display module has to meet timing requirements, which are defined for the transmitter (MCU) on MIPI D-Phy standard.

E-mail: sales@digiwise.asia

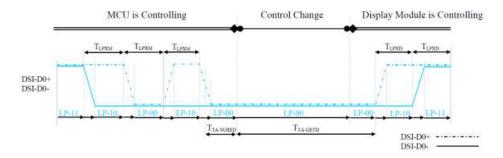

#### 7.4 Low Speed Mode - Bus Turn Around

Lower Power Mode and its State Periods on the Bus Turnaround (BTA) from the MCU to the Display Module (ILI9881C) are illustrated for reference purposes below.

BTA from the MCU to the Display Module

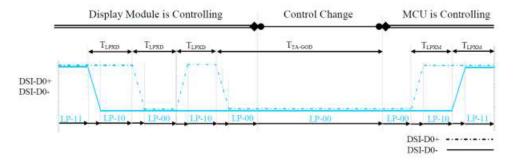

Lower Power Mode and its State Periods on the Bus Turnaround (BTA) from the Display Module (ILI9881C) to the MCU are illustrated for reference purposes below.

BTA from the Display Module to the MCU

#### Low Power State Period Timings-A

| Signal | Symbol                | Description                                                  |                   | Max                 | Unit |  |

|--------|-----------------------|--------------------------------------------------------------|-------------------|---------------------|------|--|

| DOD/N  | _                     | Length of LP-00, LP-01, LP-10 or LP-11 periods               |                   | 50                  | 75   |  |

| D0P/N  | T <sub>LPXM</sub>     | MCU → Display Module (ILI9881C)                              |                   | 75                  | ns   |  |

| DODAL  | -                     | Length of LP-00, LP-01, LP-10 or LP-11 periods               | 50                | 75                  |      |  |

| D0P/N  | T <sub>LPXD</sub>     | Display Module (ILI9881C) → MCU                              | 50                | 75                  | ns   |  |

| D0P/N  | T <sub>TA-SURED</sub> | Time-out before the Display Module (ILI9881C) starts driving | T <sub>LPXD</sub> | 2xT <sub>LPXD</sub> | ns   |  |

#### **Low Power State Period Timings-B**

| Signal | Symbol               | Description                                        |                     | Unit |

|--------|----------------------|----------------------------------------------------|---------------------|------|

| D0P/N  | T <sub>TA-GETD</sub> | Time to drive LP-00 by Display Module (ILI9881C)   | 5xT <sub>LPXD</sub> | ns   |

| D0P/N  | T <sub>TA-GOD</sub>  | Time to drive LP-00 after turnaround request - MCU | 4xT <sub>LPXD</sub> | ns   |

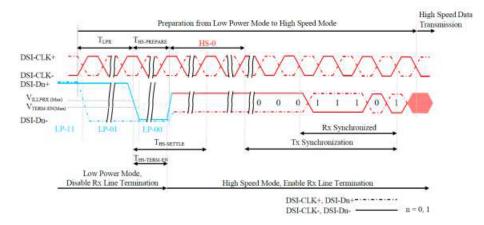

#### 7.5 Data Lanes from Low Power Mode to High Speed Mode

| Signal                                     | Symbol                                             | Description                                          |         | Max     | Unit |

|--------------------------------------------|----------------------------------------------------|------------------------------------------------------|---------|---------|------|

| DnP/N, n = 0 and 1                         | $T_LPX$                                            | Length of any Low Power State Period                 | 50      | •       | ns   |

| DnP/N, n = 0 and 1                         | T <sub>HS-PREPARE</sub>                            | Time to drive LP-00 to prepare for HS Transmission 4 |         | 85+6xUI | ns   |

| DnP/N, n = 0 and 1 T <sub>HS-TERM-EN</sub> | Time to enable Data Lane Receiver line termination |                                                      | 35+4xUI | ns      |      |

|                                            | I HS-TERM-EN                                       | measured from when Dn crosses VILMAX                 | -       | 3374301 | 115  |

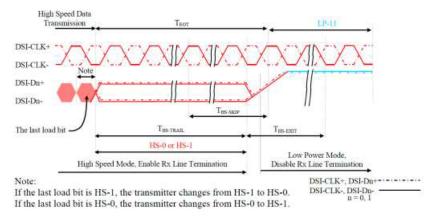

#### 7.6 Data Lanes from High Speed Mode to Low Power Mode

| Signal             | Symbol               | Description                                                              | Min | Max     | Unit |

|--------------------|----------------------|--------------------------------------------------------------------------|-----|---------|------|

| DnP/N, n = 0 and 1 | T <sub>HS-SKIP</sub> | Time-Out at Display Module (ILI9881C) to ignore transition period of EoT | 40  | 55+4xUI | ns   |

| DnP/N, n = 0 and 1 | T <sub>HS-FXIT</sub> | Time to driver LP-11 after HS burst                                      | 100 | _       | ns   |

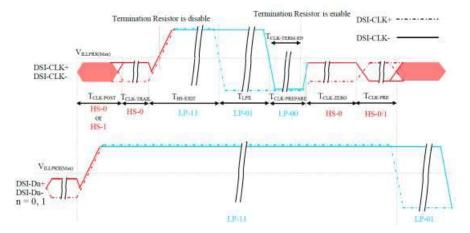

## 7.7 DSI Clock Burst - High Speed Mode to/from Low Power Mode

| Signal | Symbol                                              | Description                                                                                                             | Min      | Max | Unit |

|--------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------|-----|------|

| CLKP/N | T <sub>CLK-POST</sub>                               | Time that the MCU shall continue sending HS clock after the last associated Data Lanes has transitioned to LP mode      | 60+52xUI | -   | ns   |

| CLKP/N | T <sub>CLK-TRAIL</sub>                              | Time to drive HS differential state after last payload clock bit of a HS transmission burst                             |          | -   | ns   |

| CLKP/N | T <sub>HS-EXIT</sub>                                | Time to drive LP-11 after HS burst                                                                                      | 100      | -   | ns   |

| CLKP/N | T <sub>CLK-PREPARE</sub>                            | Time to drive LP-00 to prepare for HS transmission                                                                      | 38       | 95  | ns   |

| CLKP/N | T <sub>CLK-TERM-EN</sub>                            | Time-out at Clock Lane to enable HS termination                                                                         | •        | 38  | ns   |

| CLKP/N | T <sub>CLK-PREPARE</sub><br>+ T <sub>CLK-ZERO</sub> | Minimum lead HS-0 drive period before starting Clock                                                                    | 300      | -   | ns   |

| CLKP/N | T <sub>CLK-PRE</sub>                                | Time that the HS clock shall be driven prior to any associated<br>Data Lane beginning the transition from LP to HS mode | 8xUI     | -   | ns   |

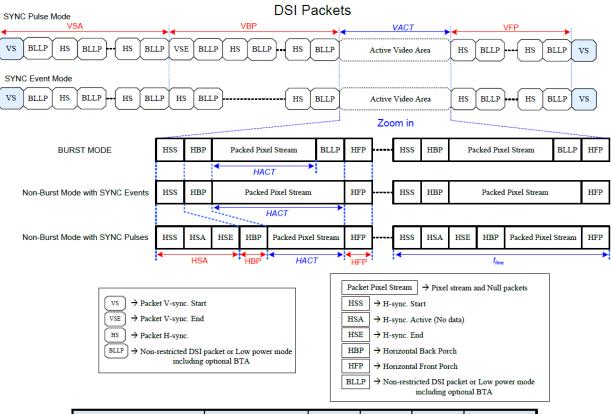

#### 7.8 Timing for DSI video mode

| Parameters              | Symbols           | Min.        | Тур. | Max.   | Units     |

|-------------------------|-------------------|-------------|------|--------|-----------|

| Vertical sync. active   | VSA               | 2 (Note 6)  | -    | -      | Line      |

| Vertical Back Porch     | VBP               | 14 (Note 6) | -    | -      | Line      |

| Vertical Front Porch    | VFP               | 8 (Note 6)  | -    | -      | Line      |

| Active lines per frame  | VACT              | -           | 1280 | -      | Line      |

| Horizontal sync. active | HSA               | 2           | -    | -      | Pixel     |

| Horizontal Porch period | HSA + HBP + HFP   | 1.6         | -    | -      | us        |

| Active pixels per line  | HACT              | -           | 720  | -      | Pixel     |

| Bit rate                | BR <sub>bps</sub> | 385         |      | Note 5 | Mbps/lane |

1 UI=1/Bit rate

HSA(pixel)= (tHSA\*lane number ) / (UI\* pixel format )

HBP(pixel)= (tHBP\*lane number ) / (UI\* pixel format )

HFP(pixel)= (tHFP\*lane number ) / (UI\* pixel format )

$$\label{eq:rate_problem} Frame \ Rate = \frac{BR_{bps} \ x \ Lane_{num}}{(VACT+VSA+VBP+VFP) \ x \ (HACT+HSA+HBP+HFP) \ x \ Pixel \ Format}$$

Example:  $BR_{bps} = 457Mbps/lane$ , 1UI=2.1883ns, Frame rate=60Hz, VACT=1280, VSA=2, VBP=30, VFP=20, HACT=720, HSA=33, HBP=100, HFP=100, Lane\_{num}=4(lane), Pixel Format=24(bit).

## 7.8.1 TFT Timing

| Signal | Parameter       | Symbol | Min. | Тур.  | Max. | Unit. | Remark |

|--------|-----------------|--------|------|-------|------|-------|--------|

| DCLK   | CLK frequency   | Fclk   | 50   | 66.77 | 80   | MHz   |        |

|        | Horizontal Line | Th     | 825  | 880   | 1056 | CLK   |        |

|        | HS Display Area | Thd    | -    | 800   | -    | CLK   |        |

| HSYNC  | HS Pulse Width  | Thpw   | 4    | 16    | 20   | CLK   |        |

|        | HS Back Porch   | Thb    | 8    | 48    | 88   | CLK   |        |

|        | HS Front Porch  | Thfp   | 2    | 16    | 28   | CLK   |        |

| VSYNC  | VS Period Time  | Tv     | 1288 | 1296  | 1330 | th    |        |

|        | VS Display Area | Tvd    | -    | 1280  | -    | th    |        |

|        | VS Pulse Width  | Tvpw   | 2    | 4     | 6    | th    |        |

|        | VS Back Porch   | Tvb    | 2    | 4     | 10   | th    |        |

|        | VS Front Porch  | Tvfp   | 2    | 8     | 10   | th    |        |

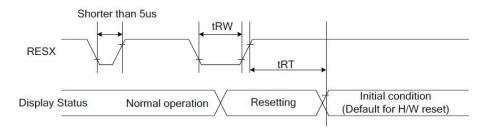

#### 7.9 Reset Timing

Figure 124: Reset Timing

Table 47: Reset Timing

| Signal | Symbol | Parameter            | Min | Max              | Unit |

|--------|--------|----------------------|-----|------------------|------|

|        | tRW    | Reset pulse duration | 10  |                  | uS   |

| RESX   |        |                      |     | 5 (note 1,5)     | mS   |

|        | tRT    | Reset cancel         |     | 120 (note 1,6,7) | mS   |

#### Notes:

- The reset cancel also includes required time for loading ID bytes, VCOM setting and other settings from EEPROM to registers. This loading is done every time when there is H/W reset cancel time (tRT) within 5 ms after a rising edge of RESX.

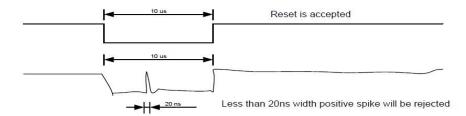

- 2. Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the Table 48.

Table 48: Reset Descript

| RESX Pulse           | Action         |

|----------------------|----------------|

| Shorter than 5us     | Reset Rejected |

| Longer than 10us     | Reset          |

| Between 5us and 10us | Reset starts   |

- During the Resetting period, the display will be blanked (The display enters the blanking sequence, which

maximum time is 120 ms, when Reset Starts in the Sleep Out mode. The display remains the blank state in the

Sleep In mode.) and then return to Default condition for Hardware Reset.

- 4. Spike Rejection can also be applied during a valid reset pulse, as shown below:

Figure 125: Positive Noise Pulse during Reset Low

- 5. When Reset applied during Sleep In Mode.

- 6. When Reset applied during Sleep Out Mode.

- It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

#### 8. OPTICAL CHARACTERISTICS

| Iter          | n          | Symbol       | Condition                      | Min.  | Тур.  | Max.  | Unit              |  |

|---------------|------------|--------------|--------------------------------|-------|-------|-------|-------------------|--|

| Brightness    |            |              |                                | 360   | 450   |       | cd/m <sup>2</sup> |  |

| Unifor        | mity       | B-uni        | Note1,                         |       | 80    |       | %                 |  |

| Contrast      | Ratio      | CR           | Note 3, $(\theta = 0^{\circ})$ | 1200  | 1500  |       |                   |  |

| Response Time |            | Tr+Tf        | $\theta = 0$ , Normal          |       | 30    | 35    | ms                |  |

| Color         | \//bi+a    | Wx           | Viewing                        | 0.260 | 0.310 | 0.360 |                   |  |

| Chromaticity  | White      | Wy           |                                | 0.275 | 0.325 | 0.375 |                   |  |

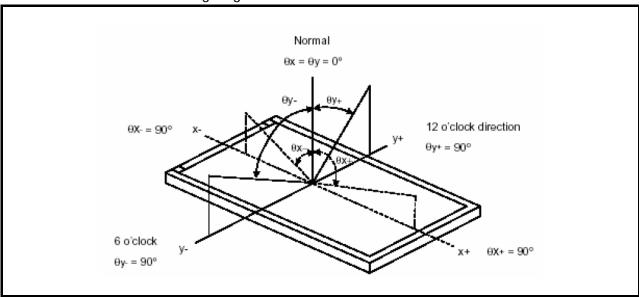

|               | Horizontal | heta x+      |                                | 75    | 80    |       |                   |  |

| View angle    | попідопіа  | heta x-      | Center                         | 75    | 80    |       |                   |  |

|               | Vertical - | θ <b>Y</b> + | CR≥10                          | 75    | 80    |       |                   |  |

|               |            | <i>θ</i> Y-  |                                | 75    | 80    |       |                   |  |

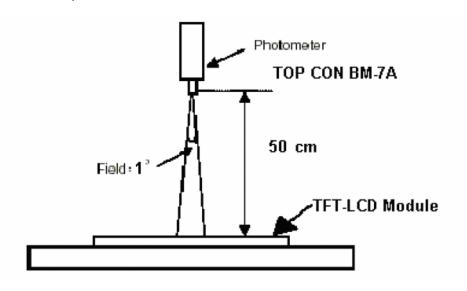

Note: The following optical specifications shall be measured in a darkroom or equivalent state(ambient luminance  $\leq 1$  lux, and at room temperature). The operation temperature is  $25^{\circ}C\pm2^{\circ}C$ . The measurement method is shown in Note1.

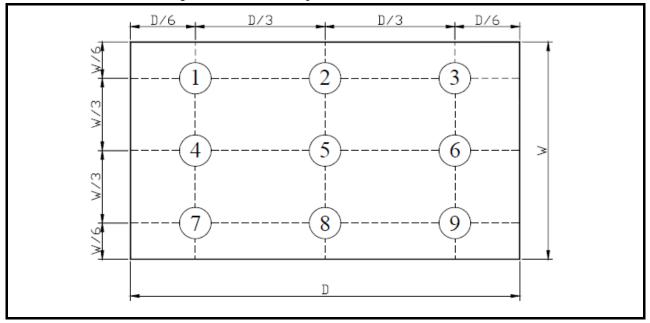

Note1: The method of optical measurement:

Note2: Measured at the center area of the panel and at the viewing angle of the  $\theta x = \theta y$ =0°

Note3: Definition of Contrast Ratio (CR):

CR = Luminance with all pixels in white state ÷ Luminance with all pixels in Black state

Note 4: Definition of Viewing Angle:

Note 5: Definition of Brightness Uniformity (B-uni):

B-uni = (Minimum luminance of 9 points÷Maximum luminance of 9points)X100%

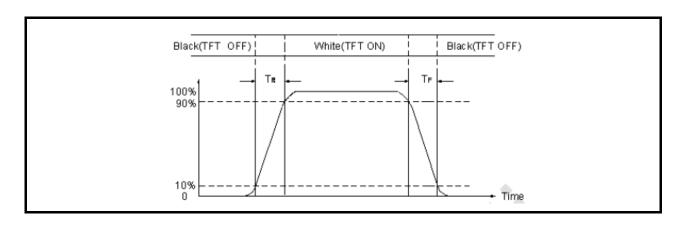

## Note 6: Definition of Response Time:

The Response Time is set initially by defining the "Rising Time (Tr)" and the "Falling Time (Tf)" respectively. Tr and Tf are defined as following figure

## Note 7: Definition of Chromaticity:

The color coordinates (Wx,Wy),(Rx,Ry),(Gx,Gy),and (Bx,By) are obtained with all pixels in the viewing field at white, red, green, and blue states, respectively.

E-mail: sales@digiwise.asia

#### 9. RELIABILITY

#### 9.1 Test Condition

9.1.1 Temperature and Humidity(Ambient Temperature)

Temperature :  $25 \pm 5^{\circ}$ C Humidity :  $65 \pm 5\%$

#### 9.1.2 Operation

Unless specified otherwise, test will be conducted under function state.

#### 9.1.3 Container

Unless specified otherwise, vibration test will be conducted to the product itself without putting it in a container.

#### **9.1.4** Test Frequency

In case of related to deterioration such as shock test. It will be conducted only once.

#### 9.2 TESTS

| No. | ITEM                            | CONDITION CRITERION                        |  |  |  |  |  |

|-----|---------------------------------|--------------------------------------------|--|--|--|--|--|

| 1   | High Temperature Storage        | 70°C, 120 hrs                              |  |  |  |  |  |

| 2   | Low Temperature Storage         | -20°C, 120 hrs                             |  |  |  |  |  |

| 3   | High Temperature Operating      | 60°C, 120 hrs                              |  |  |  |  |  |

| 4   | Low Temperature Operating       | -10°C, 120 hrs                             |  |  |  |  |  |

| 5   | High Temperature/Humidity       | 40°C, 90%RH, 120 hrs                       |  |  |  |  |  |

|     | Non-Operating                   | 40 G, 70/m(11, 120 1113                    |  |  |  |  |  |

| 6   | Temperature Shock Non-Operating | -20°C ←→ 70°C                              |  |  |  |  |  |

|     | remperature shock Non-operating | (0.5hr each), 25 cycles                    |  |  |  |  |  |

|     |                                 | Frequency:0 ~ 55 Hz Amplitude:1.5 mm       |  |  |  |  |  |

| 7   | Vibration Test Non Operating    | Sweep Time:11min                           |  |  |  |  |  |

| ′   | Vibration Test Non-Operating    | Test Period:6 Cycles for each Direction of |  |  |  |  |  |

|     |                                 | X,Y,Z                                      |  |  |  |  |  |

Note1: The test sample have recovery time for 24 hours at room temperature before the function check. In the standard conditions, there is no any touch panel function NG issue occurred.

#### 9.3 JUDGMENT STANDARD

The judgment of the above test should be made as follow:

Pass: Normal display image with no obvious non-uniformity and no line defect. Partial transformation of the module parts should be ignored.

Fail: No display image, obvious non-uniformity, or line defects.

E-mail: sales@digiwise.asia

## 9.4 INCOMING INSPECTION STANDARDS

| No. | Parameter           | Criteria                                                                                                 |             |          |                        |                |           |            |          |      |        |  |

|-----|---------------------|----------------------------------------------------------------------------------------------------------|-------------|----------|------------------------|----------------|-----------|------------|----------|------|--------|--|

|     |                     | Display function: No Display malfunction (Major) Contrast ratio (Black, White):                          |             |          |                        |                |           |            |          |      |        |  |

|     |                     |                                                                                                          |             |          |                        |                |           |            |          |      |        |  |

|     |                     | Does not meet specified range in the spec. (Major) (Note:3)                                              |             |          |                        |                |           |            |          |      |        |  |

|     |                     | Line Defect: No obvious Vertical and Horizontal line defect in bri<br>dark and colored. (Major) (Note:1) |             |          |                        |                |           | rignt,     |          |      |        |  |

|     |                     | Daint F                                                                                                  |             |          |                        |                |           |            |          |      |        |  |

|     |                     | Point L                                                                                                  | Defect : A  | ctive a  |                        |                | le numb   |            | iote: i) |      | T      |  |

|     |                     |                                                                                                          | Iten        | n        |                        |                |           | ei         | Tota     | al   |        |  |

|     |                     |                                                                                                          |             |          |                        |                | e Area    |            |          |      | 1      |  |

|     |                     |                                                                                                          | Brig        |          |                        |                | 2         |            | 5        |      |        |  |

|     |                     |                                                                                                          | Dar         | k        |                        |                | 4         |            |          |      |        |  |

|     |                     |                                                                                                          |             |          |                        |                |           |            |          |      |        |  |

| 1   | Operating           |                                                                                                          |             |          |                        |                |           |            |          |      |        |  |

|     |                     | Non-u                                                                                                    | niformity:  | Visible  | e thro                 | ough !         | 5%ND f    | ilter.     | (Minor   | )    |        |  |

|     |                     | Foreig                                                                                                   | n materia   | al in Bl | ack o                  | or Wh          | ite spot  | s sha      | ape (W   | >1/4 | L)     |  |

|     |                     |                                                                                                          |             | Zone     | ٨٥٥                    | ontob          | ما        | Clas       | s        | ^    | QL     |  |

|     |                     |                                                                                                          |             |          | 7,00                   | eptab<br>ımber | -         | Of         |          |      | evel   |  |

|     |                     |                                                                                                          | Dimensi     | on       | 110                    | iiibei         | ן ו       | Defec      | ts       | LC   | , v C1 |  |

|     |                     |                                                                                                          | D> 0        | .5       |                        | 0              |           |            |          |      |        |  |

|     |                     |                                                                                                          | 0.3 < D     | ≤ 0.5    |                        | 5              |           | Mino       | r        | 1    | .5     |  |

|     |                     |                                                                                                          | D ≤ 0       | 0.3      |                        | *              |           |            |          |      |        |  |

|     |                     |                                                                                                          | D = (Lon    |          |                        |                | * : Disre | _          |          |      |        |  |

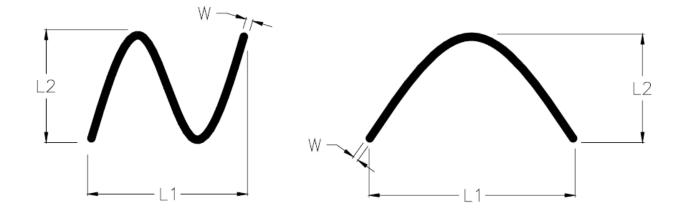

|     |                     | Foreig                                                                                                   | gn Materi   |          |                        |                | al shape  | ) (W≤      |          | •    | : 4)   |  |

|     |                     |                                                                                                          |             |          | Zone                   | •              | Accept    | able       | Clas     | - 1  | AQL    |  |

|     |                     | 1 (100                                                                                                   |             | 14//     |                        |                | numk      |            | Of       |      | Level  |  |

|     |                     | L (mi                                                                                                    | L >5        | W(mn     | /)<br>√>0.1            |                | 0         |            | Defe     | CIS  |        |  |

|     |                     |                                                                                                          | < L ≤ 5     | 0.03     |                        |                | 5         |            | Mino     | ٦r   | 1.5    |  |

|     |                     | l <del></del>                                                                                            | . ≤0.5      |          | <0.0≥                  |                | *         |            | IVIIII   |      | 1.0    |  |

|     |                     |                                                                                                          | Length      |          | <u>_</u> o.o.<br>Widtŀ |                | : Disre   | nard       |          |      |        |  |

|     |                     |                                                                                                          | nsion: Ou   |          |                        |                | . Disie   | gara       |          |      |        |  |

|     |                     |                                                                                                          | appeara     |          |                        | ,              | nor)      |            |          |      |        |  |

|     |                     |                                                                                                          | ch on the   |          |                        |                |           |            |          |      |        |  |

|     |                     |                                                                                                          |             | Z        | one                    | Acce           | pta       | Clas       | ss       | /    | AQL    |  |

|     |                     |                                                                                                          |             |          |                        | ble            | •   C     | f Def      | ects     | L    | _evel  |  |

|     |                     | L                                                                                                        | (mm)\       | W(mm     | _                      | numb           | per       |            |          |      |        |  |

|     |                     |                                                                                                          |             | W>0      | .1                     | 0              |           | Min        | or       |      | 1.5    |  |

|     |                     |                                                                                                          | L ≤ 3       | W≤0      | .1                     | 3              |           |            |          |      |        |  |

|     |                     |                                                                                                          |             |          |                        |                |           |            |          |      |        |  |

|     | External Inspection |                                                                                                          | : Length    |          |                        |                | : Disreg  | ard        |          |      |        |  |

| 2   | (non-operating)     | Dent o                                                                                                   | r bubble (  |          | pola                   | rıze (İ        |           |            |          |      | 1      |  |

|     |                     |                                                                                                          | Zon         | е        | Acc                    | eptab          | וםו       | ass<br>Of  | AC       | QL   |        |  |

|     |                     |                                                                                                          | Dimension   |          | nι                     | ımbeı          | r 1       | ਾ<br>fects | Le       | vel  |        |  |

|     |                     |                                                                                                          | D≤0.        | _        |                        | *              |           |            |          | _    | †      |  |

|     |                     |                                                                                                          | D≤0.        |          |                        | 3              | M         | inor       | 1.       | .5   |        |  |

|     |                     | ⊢                                                                                                        | <b>D_0.</b> | -        |                        |                |           |            |          |      | 1      |  |

|     |                     | D                                                                                                        | = (Long -   | + Shor   | t) / 2                 |                | *         | : Disi     | regard   |      |        |  |

|     |                     |                                                                                                          | , 3         |          | ,                      |                |           |            | •        |      |        |  |

|     |                     |                                                                                                          |             |          |                        |                |           |            |          |      |        |  |

|     | 1                   |                                                                                                          |             |          |                        |                |           |            |          |      |        |  |

E-mail: sales@digiwise.asia

|          |          |             | Definition                                                                     |

|----------|----------|-------------|--------------------------------------------------------------------------------|

| Class of | Major    |             | It is a defect that is likely to result in failure or to reduce materially the |

| defects  |          | 1102 0.0070 | usability of the product for the intended function.                            |

| defects  | Minor    | AQL 1.5%    | It is a defect that will not result in functioning problem with deviation      |

|          | IVIIIIOI | AQL 1.570   | classified.                                                                    |

#### Note1:

- (a)Bright point defect is defined as point defect of R,G,B with area >1/2 pixel respectively (b)Dark point defect is defined as visible in full white pattern.

- (c)Definition of distribution of point defect is as follows:

- -minimum separation between dark point defects should be larger than 5mm.

- -minimum separation between bright point defects should be larger than 5mm.

- (d)Definition of joined bright point defect and joined dark point defect are as follows:

- -Two or more joined bright point defects must be nil.

- -Three joined dark point defects must be nil.

- -Coupling of one dark and one bright point in junction is counted as one dark and bright spot with 1 pair maximum.

- -Two Joined dark point is counted as two dark points with 2 pair maximum.

Note2: The external inspection should be conducted at the distance  $30\pm$  5cm between the eyes of inspector and the panel.

Note3: Luminance measurement for contrast ratio is at the distance 50± 5cm between the detective head and the panel with ambient luminance less than 1 lux. Contrast ratio is obtained at optimum view angle.

Note4: W-Width in mm , L-length of Max.(L1,L2) in mm.

E-mail: sales@digiwise.asia

#### 9.5 Sampling Condition

Unless otherwise agree in written, the sampling inspection shall be applied to the incoming inspection of customer.

Lot size: Quantity of shipment lot per model.

Sampling type: normal inspection, single sampling

Sampling table: MIL-STD-105E

Inspection level: Level II

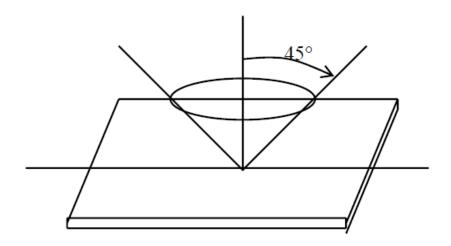

#### 9.6 Inspection conditions

The LCD shall be inspected under 40W white fluorescent light.

$\theta \leq 45^{\circ}$  inspection under non-operating condition.

$\theta \leq 5^{\circ}$  inspection under operating condition

E-mail: sales@digiwise.asia

#### 10. PRECAUTION RELATING PRODUCT HANDLING

#### **10.1 SAFETY**

- 10.1.1 If the LCD panel breaks, be careful not to get the liquid crystal to touch your skin.

- 10.1.2 If the liquid crystal touches your skin or clothes, please wash it off immediately by using soap and water.

#### 10.2 HANDLING

- 10.2.1 Avoid any strong mechanical shock which can break the glass.

- 10.2.2 Avoid static electricity which can damage the CMOS LSI—When working with the module, be sure to ground your body and any electrical equipment you may be using.

- 10.2.3 Do not remove the panel or frame from the module.

- 10.2.4 The polarizing plate of the display is very fragile. So , please handle it very carefully, Do not touch, push or rub the exposed polarizing with anything harder than an HB pencil lead (glass , tweezers , etc.)

- 10.2.5 Do not wipe the polarizing plate with a dry cloth, as it may easily scratch the surface of plate.

- 10.2.6 Do not touch the display area with bare hands, this will stain the display area.

- 10.2.7 Do not use ketonics solvent & aromatic solvent. Use with a soft cloth soaked with a cleaning naphtha solvent.

- 10.2.8 To control temperature and time of soldering is  $280 \pm 10^{\circ}$ C and 3-5 sec.

- 10.2.9 To avoid liquid (include organic solvent) stained on LCM.

#### 10.3 STORAGE

- 10.3.1 Store the panel or module in a dark place where the temperature is 25°C ± 5°C and the humidity is below 65% RH.

- 10.3.2 Do not place the module near organics solvents or corrosive gases.

- 10.3.3 Do not crush, shake, or jolt the module.